LMK04828B Digital Lock Detect 和 frequency calibration

时间:10-02

整理:3721RD

点击:

大家好,LMK04828b 的Digital Lock Detect 和 frequency calibration有联系不? Digital Lock Detect 只与寄存器PLL_2WND_SIZE 和 PLL2_DLD_CNT有关,

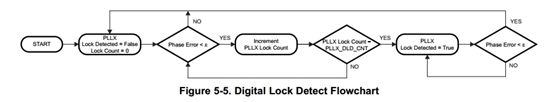

1. 对于PLL_WND_SIZE 只能是3.7ns,PLL2_DLD_CNT如何设置呢或者根据什么设置呢,Digital Lock Detect是对PLL2的输入和输出时钟进行校准,对于datasheet的Digital Lock Detect 原理不是很明白,和其他的PLL锁相环设置原理不一样吗?如下图:PLL2_DLD_CNT 是输入输出时钟的相位比较次数,但PLL_WND_SIZE是输入输出时钟的相位差,为什么小于3.7ns 还要继续比较呢?

2. frequency calibration 相关的寄存器设置时PLL2_N_CAL,它是如何设置呢,是等于PLL2_N,frequency calibration是对VCO进行校准的?

当PLL的输入参考时钟(R路径)与返馈时钟(N路径)之间的相位差达到PLL_WND_SIZE的时候,一个计数过程就开始了,当计数值达到PLL2_DLD_CNT的时候,就认为PLL进入锁定状态,Status_LD = H