SN74LS374DW锁存器不能锁存数据解决办法

时间:10-02

整理:3721RD

点击:

续上一问题,现解决了,SN74LS374不能锁存数据问题 。

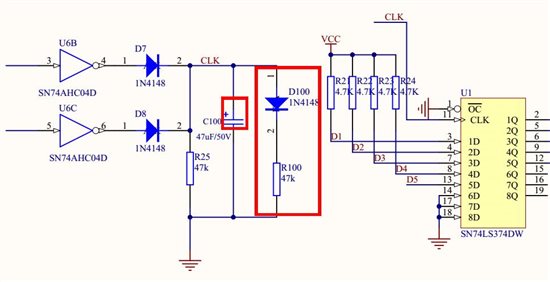

解决办法如下:在CLK对地处添加电容C100(47UF),D100与R100为放电而放置(没有这支路也同样可以锁存数据)。

但出现新问题 :初次上电,锁存器输出端1Q-4Q,都被拉为低电平,这不符合逻辑。用示波器测过,CLK上电瞬间从0V跳变至400mV。望TI工程师支招。

为啥不用“或门”呢?

WEN JAMES 于 2014-5-14 12:53 发表了以下帖子 :

为啥不用“或门”呢?

现在不是线与电路的问题,而是SN74LS374的问题,为什么会上电瞬间1Q-5Q就会输出低电平,输入端明明用电阻上拉了。

感觉没必要增加D100、R100,R25应该就能够起到放电的作用。

为什么会上电瞬间1Q-5Q就会输出低电平,输入端明明用电阻上拉了----------D端的数据只有在CLK的时候才会反映到Q端。

上电初态是不定的吧

Q: 现在不是线与电路的问题,而是SN74LS374的问题,为什么会上电瞬间1Q-5Q就会输出低电平,输入端明明用电阻上拉了。

A: 上电瞬间输出为低或为高这个是PU3S电路的特性,简单来说,3态输出的器件内部集成了PU3S(Power-Up 3-State)电路,目的是为了保证上电瞬间输出为一个有效的逻辑电平和掉电瞬间输出为高阻抗的状态。 你可以参考下附件应用手册的Page21有关Pu3S的介绍。7144.szza036b.pdf