CDCE62002配置问题以及锁定

您好,我自己设计的PCB上现在用CDCM61004和CDCE62002两级PLL级联得到所需的500M时钟,CDCM61004为前级输出125M LVDS时钟作为CDCE62002的输入,输出需要500M LVDS时钟。目前的问题是,前级125M输出正常,在后级配置完CDCE62002的register0,1后,只能输出400M左右时钟,而且PLL 未锁定。配置为250M时钟只能输出200M左右,125M输出只能100M左右,而且都不能锁定。是寄存器配置不对吗?还是loop filter我只配置了internal,外部EXT_LP悬空未接,然后前级125M输出jitter大了造成不能锁定?现在很困惑,找不到问题在哪里,期盼尽快得到解答,非常感谢。

能否提供下你具体的寄存器配置吗?从你的输出不对看,是不是哪里参数配置超出了规定。

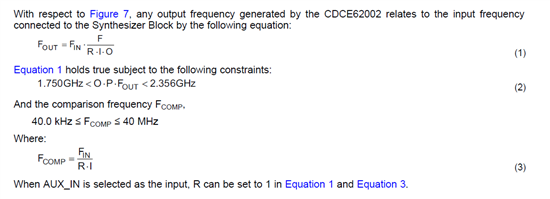

你按下面的确认下是不是在范围之内:

首先,谢谢您的关注。配置寄存器时确实按照datasheet的要求来的,当想得到125M输出时,配置寄存器register0=32'h5440_1150,register1=32'h8387_e021,故R=5,I=2,F=80,P=2,O=8,输入时钟为125M,所以Fvco=2000MHz,Fcomp=12.5MHz.当配置500M输出时钟时,register0=32'h5110_1150只把O=2,而register1=32’h8387_e021保持不变。

所以目前看来寄存器配置中的R、I、F、P、O这些应该是没出错的,其他的模式配置等是按照default或EVM6670开发板设置的,用SPI总线配置CDCE62002的代码用的也是开发板给出的参考设计

所用得配置是否在cdce62002evm验证过?把完整gui配置的截图是否发来 看下

并没有在6670开发板上验证过,我这边没有开发板,只是用了它的CDCE62002的参考设计做了稍稍改动用在我自己的设计中。

没有开发板,所以不能提供GUI的配置图。上个附件图片是register0的配置,这个是register1的配置。

我的时钟芯片现在能锁定并能输出500M LVDS时钟了,现在来完善下我提出的问题。开发板6670给出的参考设计是没问题的,很完美。我在电路设计上犯了个错误,级联的两级PLL,前一级的CDCM61004的输出模式应该配置成LVDS,我的电路配置成LVCMOS,才出现上面的现象,错误犯得很低级,反省一下。。。GUI的话,没有开发板也是可以用的。

找到问题就好,之前看到你说CDCM61004是125M LVDS输出,所以都没有往这方面想。

你好!小弟最近也在用CDCE62002芯片,能否共享该芯片的参考设计程序?感激不尽。

可以下载CDCE62005的EVM GUI软件,根据实际要求,将输入输出频率设置好,将滤波器的参数设置好,然后通过GUI里面的Tools-download the firmware to EVM。可参考EVM user's guide Page5的关于GUI的使用步骤: http://www.ti.com/lit/ug/scau034/scau034.pdf

EVM GUI可通过以下链接下载:http://www.ti.com/lit/zip/scac112