请教一下为什么LMK04906 用于双锁相环时PLL1无法锁定呢?没有LOS和DAC告警,显示DAC未锁定,PLL1 DLD为低,多谢指导

请教一下为什么LMK04906 用于双锁相环时PLL1无法锁定呢?没有LOS和DAC告警,显示DAC未锁定,PLL1 DLD为低,芯片是直接在EVB上工作的,多谢指导

你得EVM哪个得来的,新的么?如果是EVM锁不定,可能是配置或者连接有问题,

请把你的配置放上来,参考是哪个口给的,参考选择是否正确?

你好,配置见附件

链接方式是前一个LMK04906作为后一个LMK04906的输入,后一级1通道作为输入,附件是后级的 配置,

两个LMK04906都是EVM板上自带的,从TI订购的,多谢~

顶上

你一级环参考是61.44M么?用codeloader打开你的配置后显示锁25M, 但是evm上的VCXO原装是122.88.你确认夏

建议你把coderloader截图贴上来,另外把监相器相位反一下试.

上级是61.44M。我们购买单板上焊接的是25M vcxo,我们原来也以为是122.88M,结果不是的。

刚才测试了一下refrence和out相位,实际是锁上的,但是DAC LOCKDE 和PLL1 DLD还是低,这两个寄存器的判断条件是?现在已经把PLL1_WND_SIZE设置为最大40ns,PLL1_DLD_CNT=1了,coderloader截图在附件中,谢谢

是两块板第一块板能锁,第二块板不能锁么?

你得参考是从clock0输入么?如果是单端输入需要把输入接口设置为CMOS.

你好,

第一块单板没有输入,肯定锁不上,

第二块单板从第一块引入refrence,是差分的信号,测试该单板的输入和输出,发现是锁上的,但是PLL1_DLD和DAC_LOCKDE寄存器显示是低的,这个是怎么回事呢?

谢谢

你好,你目前的测试环境有如下问题:

1.第一块板没有锁定,如何给第二块板作为参考呢?这个没有锁定的时钟是不稳定的.

2.无法只看输出就确定是锁上的,锁定要看锁定指示,就算输出与输入一致,锁定指示没有锁定时间长了也会飘和抖动。

另外lmk04906的evm默认vcxo是122.88M,见下面文档, 建议与你的供应商联系确认是否被修改过;

http://www.ti.com/lit/ug/snau126/snau126.pdf

建议按照正常流程进行测试:

利用信号源提供稳定参考使第一块板可靠锁定,单板正常后再去测试第2块板

谢谢

好的

我想问一下PLL1_DLD和DAC_LOCKED的判决条件是?

要保证你参考频率被识别,并经过R divider后与VCXO经过N divider后进入监相器频率一致,环路的设置正确能才能锁定,DAC是用于Holder over的,

另外从你得截图上看上去参考选的是CLKin1但是只有CLKin0和CLKin2是enable的.需要你确认

你好

VCXO会询问供货商。 现在将问题清晰一下:

1. 两块板, 第一块板配置成Force Holdover+MAN DAC模式,将输出频差调整到与第二块板相差30ppm之内

2. 第二块板从CLKin1进, 配置成CMOS.第二块板配置成Dual PLL internal VCO模式

示波器trigger在输入上看CLKout, 两者锁定(有固定相差, 但有3ns左右wander)

PLL1 DLD配置为 PLL1_WND_SIZE=40ns PLL1_DLD_CNT=2 从LD Status中输出。 PLL1 DLD一直未被置起

观测DAC Lock已置起

你好,我想再问一下 DAC Locked is asserted when EN_Track = 1 and DAC is closely tracking the PLL1 tuning voltage.中的closely具体是一个什么数值?偏差小于多少可以锁定?多谢~

1.建议你先确认单板是否能好的够正常能够锁定,因为看上去被改过.

2.你得截图上CLKin1没有enable.

3. 你这是什么应用? PLL2是否能锁定?

请参考手册29页:Holdover Frequency Accuracy and DAC Performance章节相关内容,谢谢

Hi

1. CLKin_sel_MODE = CLKin1_Manual . This configuration is override EN_CLKin1

2. PLL2 是锁定状态, PLL2 DLD indicator signal is asserted

ok, 你可以作如下测试验证参考是否被识别:

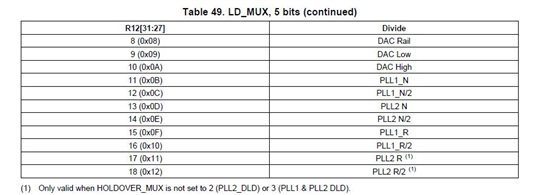

LD_MUX设置为

PLL1_R或PLL1_R/2,确认是否参考频率正确识别;

这个是对的, PLL1_R为pulse信号的pfd频率, PLL_R/2为50%duty cycle Fpfd/2

你第一块板的VCXO也是25M? 然后用二级环出的61.44M?

1.那在测下PLL1_N,如果也是对的请做下一条

2.建议直接使用25M的(或整数倍)作为参考,提高鉴相频率到5M或12.5M看是否能锁定,

附件是一个122.88锁30.72可以锁定的配置给你参考.

8664.04906locked.mac

VCXO 的整数倍可以的了, 看来是分数分频时的问题。 需要调整那些参数才能满足PLL1锁定

配置成25M倍数可以了,那是不是说只能使用25M整数倍为参考?

还有一个问题:codeloader工具只要点击界面上的SYNC_QUAL就会自动关闭,这个是怎么回事呢?谢谢~

你监相频率是多少?

参考是37.5M, 用12.5M或2.5M监相是否可以?

应该不是整数/分数,关键看你监相频率是多少?监相频率太低,你环路建立稳定时间越上,就容易导致失锁.

SYNC_QUAL会有一些相关设置, 用于一些需要动态调整digital delay同步的地方,一般用不上.

这个功能我们需要使用,请问如何解决选中SYNC_QUAL就退出codeloader的问题?谢谢

你这个是什么样的应用?

你还可以先在register页面手动修改这个寄存器: R11的bit17, 谢谢!