cdce62005的锁定范围太窄

使用cdce62005的过程中,使用默认配置,发现其在25M参考时钟输入的情况下不能锁定,只能在23.9-24.8MHz的参考时钟输入范围内锁定。

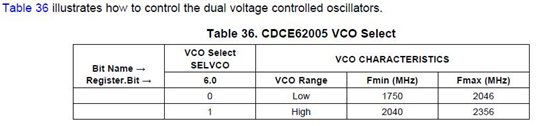

这个锁定范围太窄,而且由此反推出的cdce62005的low range的VCO频率范围为远远达不到手册上所给出的1750-2046MHZ。

刚刚看到一位ying wang用户也遇到了类似的问题。期盼贵公司的专家能够帮忙指出出现这个问题的原因。

补充新发现的两个现象,希望对上述问题有所帮助。

1、为了解决上述问题,使用了读命令来读出cdce62005中的9个寄存器的数据,验证SPI接口的正确性。测试发现,读出来的数据是正确的,但令人疑惑的是,按照手册上所给,在32bit的命令字中,低4bit(即第0~3bit)为1110,即表示这是一个读命令;然后第4~7bit应该表示读的哪一个寄存器。但实际上,第5~8bit反而标示了读的寄存器的序号,第4bit为1或者为0结果都相同。

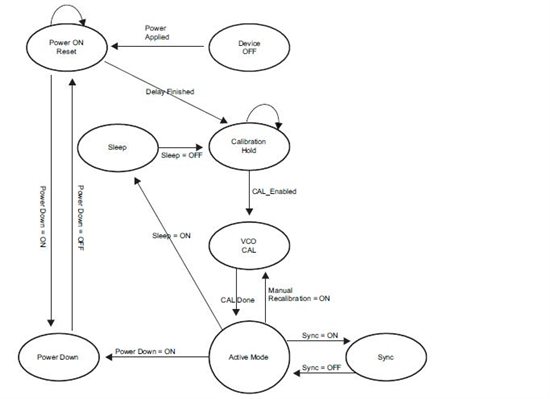

2、手册上VCO的流程中有一个Calibration Hold。将ENCAL_MODE设置为1,ENCAL设置为0,这样的话按照流程所述应该始终处于Hold状态,除非往ENCAL写入一个1。将该配置数据更新到cdce的内部EEPROM中(更新是成功的,已通过1中的读出验证)。但每次上电后,cdce62005仍然直接从Calibration Hold跳到VCO CAL然后进入Active Mode了(因为cdce直接显示锁定,并有信号输出)。不知为何。

你好,CDCE62005在国内应用非常广, 你同样可以参考ying wang问题的相关答复:在改变参考频率后请按照手册上的流程计算并修改配置,以及校准。

简单的解释就是VCO可理解为一个无稳态多谐振荡器, 给vco提供一个新的校准电压和校准字,从而让VCO在一个新的频率上锁定并稳定的重新震荡起来.

不知道我的回答是否解释你的问题?

我觉得您应该先解释一下为何在默认的配置下(没有修改配置),cdce62005不锁定在25MHz。我们目前并没有改变参考频率。

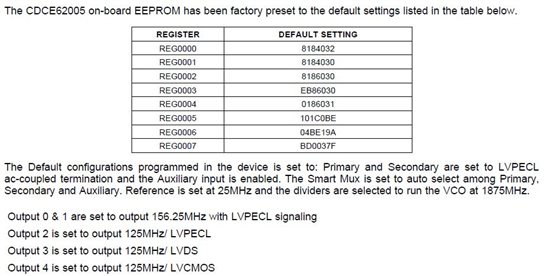

CDCE62005内部EEPROM的出厂默认配置手册23页如下,是25M输入的,三个端口自动选择。

只要你按照手册36页上电顺序进行操作应该就可以正常工作的。如果还是无法出信号,可以用输出选择到参考mux选择确认25M时钟是否进入内部模块

已经验证输出到参考mux,输出时钟等于输入时钟,说明25M已经进入了内部模块。

上电顺序power down管脚按照要求在上电后维持了50us的低电平。power on后的状态跳转在出厂配置下应该是自动完成的,还需要再控制吗?

另外,有一点要突出一下,出厂配置下,输入24MHz时,cdce62005是可以锁定的,但25MHz时是不能锁定的。

信号源什么型号,频点是用频谱仪测定的么?请根据手册23页上面的表格确认62005内部的8个寄存器值与上面表格的默认一致.

同时也可以使用62005EVM板进行交叉验证, EVM板上AUX IN可以接一个25M的晶振,可以直接锁定.

您好!

信号源是tektronix的AFG3102,频点直接设置就可以了,也用Tektronix的示波器检验过,频率时正常的。62005内部寄存器的值我已经用读上来了,与默认的配置一致。

正如上一篇帖子ying wang用户的“cdce62005锁定频率不一致”所说。在他那个开发板上,如果改变参考频率的话,VCO应该能在它手册的这个范围内变化才对啊。当它超出这个范围时才会失锁,但是现在问题是VCO在它范围里面也会失锁。这个范围实际上是某一个频段的范围,并非两个频段。

您当初给的答案是不同频段VCO需要重新calibration,但VCO本身就两个频段,他这个就是工作在某一个频段里,还需要calibration么?

请注意ying wang用户的EVM板在25M参考下是可以正常锁定的,他改了频率不锁定是因为没有改变配置并calibration。从正常流程上讲每改变一次频率或配置都需要calibration。

我跟他的问题都是VCO的锁定范围太窄,只不过他能锁定的那个窄范围刚好包括了25M,而我的没有包括,反而在24M锁定。

我不理解您说的改了频率不锁定是因为没有改变配置并calibration,假定我一开始锁定在25M,那我改变频率到25.1M,还需要重新配置并calibration?锁相环没有跟踪过程么?

他的问题其实跟你不一样的,他是在改变了参考频率导致VCO超出了一定的谐振范围又没有重新calibration而不锁定。你用软件可以看到,改变不同的频率校准后其校准字是不一样的。而你的问题是25M本身就不能锁定。

你将25M频率只增加0.1M,那你期望的vco和输出频率是多少?

在一个很小频率范围内即使不重校准PLL也能跟上,但这不是一个标准的配置使用流程。

您好!非常感谢您耐心的知道。

您的意思,这个锁相环在一个配置下只能在一个频率点锁定?

或者说您所说的VCO的调谐范围到底有多宽?是器件手册上给的范围吗?

重新calibration是重新计算参数并配置还是?校准字是各个寄存器的值吗?

如果一个配置能适用所有的频点那又何须再去配置他呢?VCO的范围在手册第一页有写具体61页如下,请按照手册36页正常流程配置工作,请你相信手册相信TI相信自己;

在calibration请仔细看33页Reigster 6 ENCAL.校准字结果在第Register8,CALWORD中。

建议你先从CDCE62005EVM和软件入手,连接如下:

http://www.ti.com/tool/cdce62005evm

您好! 不知道是否是因为沟通的问题,还是我们描述的不够清楚。

直接说来,您所说的”改变参考频率导致VCO超出了一定的谐振范围“这个命题是不成立的,在ying wang用户的帖子中,根据默认配置,根据手册上的VCO的调谐范围,输入信号频率的锁定范围绝对不仅仅在24.6MHz~25.6MHz。举个例子,在26MHz时,您可以算一下,按照默认的配置,输入26MHz时,VCO是不是超出手册上给出的调谐范围了。明显是没有的。

所以还是希望您能计算一下理论上62005的锁定范围,我觉得这并不应该是配置的问题。而我和ying wang都遇到的锁定范围太窄,虽然我的锁定范围里没有25M。

您好! 再次感谢您的关注。

不知道是否是因为沟通还是我们描述的不够清楚。

直接说来,您所提到的”改变参考频率使得VCO超出一定的调谐范围“这个命题是不成立的。在Ying Wang用户的帖子里,根据默认配置,根据手册上VCO的调谐范围,62005的锁定范围绝对不仅仅是24.6MHz~25.6MHz。举个例子,输入26MHz时,您可以计算一下,按照默认配置,对应的VCO频率不可能超过手册上给的调谐范围。但此时62005没有锁定。我想,这应该是问题的关键吧。

所以还是希望再麻烦您一次,计算一下62005在默认配置下理论上的锁定范围,您应该会有所发现。我和ying wang用户都是遇到了锁定范围太窄的问题,只不过我的锁定范围里没有包括25MHz。

你好,手册23页默认配置参考是使用的25M的, 不要在PLL工作的时候去改变参考频率以得到不同的输出频率。请你放心此芯片国内用量是很大的,建议你使用CDCE62005 EVM Control Software Installer软件和evm板进行正确的配置操作流程以得到你想要得频率,这样可以保证你在使用中不会出现异常操作。至于你为何连默认配置都无法锁定在25M建议你对照EVM进行测试,以确认是环境问题还是单板问题。

您好! 默认配置无法锁定在25MHz的情况我们会继续进行测试。

我们一直讨论的问题更关键的是62005的锁定范围是多少? 您能给个理论范围么? 按照手册上VCO的调谐范围。这个范围对应用是很重要的。谢谢

需要62005锁定,你需要设置合适的参考分频,反馈分频和预分频得到一个合适监相频率,再设置一个合适带宽的环路滤波器等并进行配置。vco如前文手册第一页所说,但是需要你用正确的方法去使用,所以推荐你从用evm入手

我一直说的就是默认配置下,62005的锁定范围。可否不要一直回避这个问题,您能先给出这个参数么? 多谢。

默认配置参数参考是25M,不存在什么锁定范围,你所说的范围应该叫做频率精度,一般要求10PPM参见手册68页, 跟环路带宽特性有关, 你觉得我的回答是否清晰?

您好,不是频率精度,简单来说,是指在默认配置下,锁相环能保持锁定时,输入信号的频率范围。

这个参数是锁相环动态性能里的一个指标,锁相环的动态性能包括:锁定时间(Lock time),捕获范围(Capture range),锁定范围(Hold range)等。我们比较关注锁定范围。

不知道这样说您是否能明白我的意思了。

也就是输入信号的频率范围误差阿,你想一个环路参数输入很宽的频率范围都能锁定是不可能的,这个主要取决于环路带宽特性,在10~50PPM内是没有任何问题的. 如果你需要更宽,可以适当放宽环路参数但是这会影响时钟性能

环路带宽特性是通过影响环路噪声和VCO噪声从而影响抖动性能的。您说的意思应该是输入信号的频率精度在10~50ppm范围内时,合理的选择环路带宽,抑制噪声,从而使得输出信号频率精度更高。这都是针对某一个频率点而言的。

我所说的锁定范围不涉及其频率精度,您可以直接当成为理想的输入信号频率。因为我并不是要求输入信号频率范围很宽时,输出信号频率还保持不变,我们考虑的是锁相环锁定之后的跟踪过程。

可是监相频率也发生了变化啊,所以环路就变了。所以这主要取决于环路特性,而不是之前你所说的VCO范围。同时在改变频率之后建议calibration校准.

环路带宽是跟相位噪声相关的,环路带宽选择合适,锁相环内部各个部件自身的噪声将被滤除,那么输出信号的抖动性能久越好。现在,我们就先不考虑相位噪声,或者说不要求锁相环能有很高的抖动性能,假定锁相环的所有部件都是理想的,输入信号频率也是理想的,没有噪声存在,环路带宽的选取还有影响么?

我指的锁定范围就是理想条件下的,这个时候锁相环的锁定范围当然就跟VCO的调谐范围有关了。VCO调谐范围越大,锁相环能锁定的输入信号频率范围也越大,其跟踪能力越强。不知道您是否认同这个观点?

那么,如果说考虑了相位噪声,改变输入信号频率,输入到VCO的控制电压随之变化,只要VCO的输出频率经过反馈分频后还能够与输入信号频率相同,那么最多输出信号的抖动性能变差,锁相环应该还是锁定的。

环路参数里面有一项叫做相位裕度phase margin的,如果相位裕度减小锁定时间lock time会变长,但是PLL不会一直等下去,有一个时间窗,当超过这个时间后就判断为失锁,不会再去锁定了.不知道你明白了没有?

是不是可以这样理解:

理想条件下,锁相环能够理想的跟踪,所以锁定范围是由VCO的频率范围决定的? 这个概念对不对?

但是实际上,因为相位裕度的存在,当输入信号相位变化的时候,环路失锁的概率增加。所以说,并不是VCO频率范围足够,就能够锁定了。也就是说我们所测到的非常窄的锁定范围是正常现象。

那我们要用的就是这个锁定范围,在改变参考频率的时候,是不可能来改变配置的。按照目前的结果,如果1个配置下,我想输入24M~26M都能锁定是不能实现的了?

如果你认为理想条件下的锁相环是不需要loop filter的那你的想法可以的,

如前文所说具体范围你可以用我们的软件计算环路特性以及EVM进行测试.不同条件下的结果可能是不一样的,谢谢!

您好! 非常感谢您的关注。叨扰了您这么久。

loop filter是肯定需要的,不然鉴相器输出没法耦合给VCO。不过可以把它看成是理想线性的就好了。

Ying Wang用户所测得的那个锁定范围是否是正常的呢?您说用软件计算特性然后进行测试,默认配置还需要计算么?我们现在要求的就是25M锁定,但是锁定范围太窄。如果说这个窄是62005芯片本身的局限,那我就没有其他问题了。

简单而言,我们就是想确认Ying Wang用户所测得的那个默认配置下的锁定范围是不是正常的现象还是测试过程中出现了问题。

如前面所说的参考变化情况下锁定时间可能还跟一些测试情况有关所以很难给出一个绝对的范围,参考频率大范围变换又不改变配置对本芯片来说不是一个正常的应用方法,比如+/-50ppm对于高性能时钟来讲已经是一个比较宽的范围了.

而你当前最大的问题在于连25M参考都无法锁定,所以建议你对比evm排查你系统异常原因

您好! 现在不锁定在25M其实对我们的应用没有什么影响,我们可以接受它锁定在24M,但是我们希望能有个2M左右的锁定范围,比如说输入24M,输出48M;然后在23M和25M的时候锁相环都能锁定,且分别输出46M和50M的信号。

根据您的说法,这种应用场合62005是无法胜任的了?

/默认配置在25M没有锁定说明的你还没有正常使用起来,这非常重要。 参考的抖动和变化快慢环路设置对锁定时间都有影响,所以无法在此给你下一个定论。所以希望你能用EVM确认环境应用。

此外如果你只是进行一个2次倍频还有一些简单的PLL供你可以参考如CDC25/5XX等系列,可以到TI官网查看,没必要用如此高端的PLL

focus.ti.com/.../parametricsearch.tsp

我知道您的意思。我不是说我这边的范围,我是指Wang Ying用户测量的范围。他们不是用EVM板测量的嘛,那他所得出的范围是正常的么?

说2倍只是举个例子,实际要求输出的频率在500M±50M,输入频率在10M±1M范围。

正如我上文所讲即使是EVM板的稳定锁定也会跟你输入参考变化的快慢和Jitter等环境因素相关, CDCE62005是具有抖动清除功能的高性能时钟芯片追求的是Jitter等性能,如果你没有这样的追求, TI目前有一百来种PLL, 你可以到我所推荐的PLL Buffers章节选择一个相对合适的器件,谢谢

可以举个大概的环境么?

输入参考的Jitter是很小的,直接由信号源产生,周期抖动在10ps左右。

输入参考的变化情况是这样的:在一段时间内是24M,过了一段时间变成25M,相当于适用两种环境,但这两个环境下的输入参考都是固定不变的。

这样可以定锁定范围了吗? 关键我不太清楚所测量到的范围是否正确。您能给个大概的量级么?

对于高性能时钟而言10ps的抖动是比较大的了,你可以在手册第一页看到该器件的抖动为350fs.

列如我前面给你解释的判断锁定内部机理,如果在一个比较窄的频率范围的飘移也许环路能跟上,但如何保证频率变化下环路的稳定性是环路设计的一部分。这正如对于一个非正常的测试我无法给你一个其正常的答案。

如果是24到25M频率来回变化,你完全可以针对两个频率来修改配置。希望你能以科学的态度来对待技术问题,用正确的方法去使用正确的器件。

很遗憾,当前的这个项目是无法在使用过程中修改配置的,只能有一个配置。根据您的说法,这是一个非正常的使用,也就是说,62005是不适用的,它更适合用在低jitter的场合,而非宽锁定范围的场合,那么目前我们就应该考虑其他锁定范围更广的芯片,对吗?

不过其实您手边做这样一个测试是再简单不过了,配置使用默认的就好,输入一个24M的参考信号,看是否锁定,再输入一个26M的信号,看是否锁定。如此而已。我们的应用要求如此,所以也一直就是这样测试的,测试的结果显示锁定范围很窄,所以想跟您咨询确认一下,不想讨论到最后,还是没有一个明确的答案。

好了,以上是关于锁定范围的问题。

最后,因为我们还有一个高抖动要求的应用场合,要求输出1G的高抖动时钟。所以还想咨询一下,关于默认配置下25M不能锁定的问题,这是我们自己设计的电路板,不知道您能否给出一些可能存在的原因,我们是在找不出是怎么回事了,输入信号频率是可以保证的,PLL的设计完全没改,输入24M能锁定,25M反而不能锁定,诧异的很。但那24M锁定的时候,没有办法配置到1G输出的。

所以说归根到底我怀疑你24M锁定而25M不锁定是有一定是有某个地方发生了异常,比如是否信号源有设置offset,或是没有进行校准等。这就是为什么我建议你用EVM去验证进行交叉测试的原因,也有利于你对该器件的理解和掌握,希望你能仔细检查,找出错误原因。

好的。我们会继续测试,找出问题的原因。信号源是没有问题的,有可能是校准的问题。

关于锁定范围的,确定不能使用62005了吧。您能再推荐一款宽锁定范围的么?

很抱歉打扰您这么久。

好的。我们会继续测试,找出问题的原因。信号源是没有问题的,有可能是校准的问题。

关于锁定范围的,确定不能使用62005了吧。您能再推荐一款宽锁定范围的么?

很抱歉打扰您这么久。

你好,YINGWANG的问题已经解决,请参看他的最终回帖。http://www.deyisupport.com/question_answer/f/59/t/5554.aspx

更多的推荐请参考我前面一个回复的连接

若有测试及现场支持的需要请与当地代理联系,谢谢

您好! 我看到他的回帖了。

很明了,一看就懂。

也就是说,不校准的情况下62005的锁定范围确实比较窄,但参考频率改变后,随之进行校准就可以达到手册上的宽范围了。

我想您前面一直强调的也是这个思想,只不过我们这个项目是没有重新校准的机会的,所以一直纠结在不校准情况下锁定范围是不是比较窄。直到最后才能明确过来,于是放弃使用62005了。

感谢您的悉心指导! 跟您讨论获益匪浅。

感谢你对我们工作的支持,更多时钟芯片请参考下面连接

www.ti.com/.../clocks_and_timers.page

您好,我现在发现时可以锁在25M的,使用的是默认参数,但是改变了配置参数之后就无法锁定了,使用的滤波参数是用软件生成的,为什么了

我的可以锁定在25M的默认参数,但是当我需要修改参数的时候发现就有失锁的状态,是采用软件生成的环路滤波参数

changshun yuanchangshun: 你好,你配置完后是否有做校准?

此问题已被解答,请参考前面答复.如果需要提问请另建新贴,谢谢!