AD1246读写寄存器的问题

你好,最近在使用5418a连接6个ad1246,顺序进行SYS0 寄存器配置时设置采样频率20HZ(写入0x02),之后想测试配置是否成功(同时验证SPI口的通讯配置),对SYS0 寄存器进行读操作,发现读出来的数据不对,写、读操作分别为

ADC1_WDATA[0]=0x02; //Write SYS0 REG By 0x02; Data Rate =20 SPS

EXCHANGE_UCB0(0x40|0x03); //写寄存器:发送第一个地址字节(address = 03h)

EXCHANGE_UCB0( 0x00); //写的长度-1后的值(发送第二个字节)

EXCHANGE_UCB0( ADC1_WDATA[0]);

__delay_cycles( 20 );

EXCHANGE_UCB0(0x20|0x03); //读寄存器:发送第一个地址字节(address = 03h)

EXCHANGE_UCB0( 0x00); //Read REG

_NOP();

ADC1_RDATA[0]=EXCHANGE_UCB0( 0xFF);

__delay_cycles( 20 );

UCBORXBUF中读出来的分别是FF,7F,FF,7F,00,7F,理想的数据应该是0x02,不知道问题出在哪?

还有__delay_cycles( 20 )中延时的20个时钟周期对应的是主系统时钟MCLK,还是对SPI口配置的时钟信号(即对SMCLK分频后的时钟信号)?

SPI协议在上升沿锁存数据,下降沿更新数据,这是一般SPI协议的作法。但ADS1246需要在下降沿锁存数据,上升沿更新数据。这点需要注意,写个值再读出来不对,肯定是时序出问题了。

__delay_cycles( 20 )是对应主时钟MCLK的。

SPI的设置是这样的,不活跃为低电平,下降沿输出,上升沿接受数据:UCB0CTL0 = UCMST+UCSYNC+UCMSB;应该是正确的。

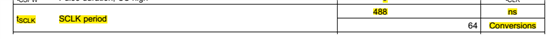

此外,对于手册7.6 Timing Requirements一节中提到的SPI接口的通信Tsclk周期限制

其中最大为周期为

| 64 | Conversions |

请问这里的Conversions指多少?例如我使用的MCLK=4.096Mhz,采样速率设置为20SPS(由于读不会寄存器的值,不确定20设置成功与否),这里的Conversions是指主时钟MCLK的周期吗?