关于JESD204B DAC配置问题

您好,我在使用DAC37J84时,遇到了一些问题,需要您的支持;具体情况如下:

我使用1片DAC37J84与Xilinx的XC7V485T FPGA进行通信,具体设置参数如下:

DAC37J84 JESD204B Setting Value

Line Rate : 1500Mbps

SYSREF : 7.5M

DACCLK : 1200M

LMFK : L=8, M=4, F=1, S=1, K=20

Frame CLK, Sampling CLK: 150M

LMFC: 7.5M

FPGA端204B核配置如下

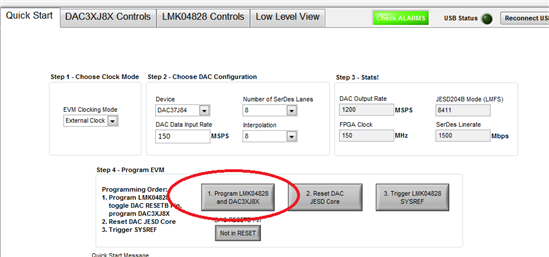

我使用DAC3XJ8X GUI v1.1软件(未连接任何设备,单独运行软件)配置界面在Quick Start点击Program LMK04828 and DAC3XJ8X按钮之后,软件自动生成了相关参数;

但是在DAC3XJ8X Controls界面的SERDES and Lane Configuration界面,LaneID的顺序是3210 7465,Which RX?顺序是32105764。此处是否正确?正确顺序是什么?

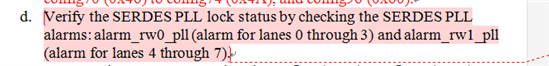

问题二:按照0116.DAC38J84 Start-up Sequence文档说明的流程进行配置时(continuous SYSREF),在回读SERDES PLL状态时,0x6C回读值一直为F00F,显示PLL未锁定,为什么?

问题三:我只配置了0116.DAC38J84 Start-up Sequence文档提到的寄存器,其他寄存器未配置,是否有问题?配置完成之后DAC无输出,syncn信号出现高低变化,我应该从哪些方面入手定位?

问题3

应该把所有寄存器都配置

很多默认寄存器的值只是保证芯片不损坏,不保证正常工作