您好,关于ADS7841第9个时钟的问题,时序图跟芯片的解释有矛盾的地方,实在讲不通

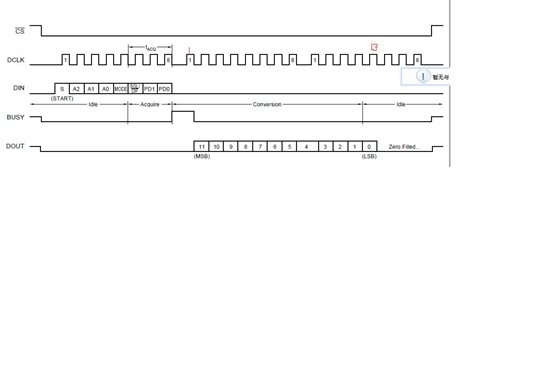

芯片资料上 figure3 和figure5中都可以看到第9个时钟,我想问下,第9个时钟跟busy的高电平是什么关系(时间上)。资料上说在时钟的下降沿输出数据,如果从第9个时钟的下降沿开始输出转换后的第11位数据的话,从第9个时钟算起,总共需要12个时钟就可以将转换后的12位数据全部输出,但是资料上又说需要一个第13个时钟才能得到输出数据的最后一位,这样就矛盾了,到底第9个时钟的下降沿 有没有转换后的数据输出?时序图上第9个时钟跟busy都重合了,那判断busy还有什么用?busy和第9时钟的时序是怎么的?

麻烦您了,希望解答。这个时序是怎么个情况?

Hi

从datasheet: http://www.ti.com.cn/cn/lit/ds/symlink/ads7841.pdf figure3 和figure5 可以看到在第八个CLK的下降沿开始BUSY输出高(DCLK Falling to BUSY Rising),而在第九个CLK的下降开始BUSY回复低。

Hi

资料上又说需要一个第13个时钟才能得到输出数据的最后一位, 请问你是在哪个资料上看到的?

结合 figure3 和figure5 可以看到,第九个SCLK用于busy信号,第十个SCLK采用出现第一个有效位,按照第十二位输出,加上第九位就是第十三位得到最后一位有效数据。(也就是说第9个时钟的下降沿没有得到有效数据)

是需要13个clock,从Figure3的时序图上可以看到,从第9个clock的下降沿开始采样,到第10个clock的下降沿MSB采样完成,到LSB的下降沿一共有13个clock。

datasheet 第十页右下角写的需要第十三个时钟,“A thirteenth clock cycle is needed for the last bit of the conversion result。”您可以自己查看下。数据采集我们已经完成了,跟您说的不一样,我们是第9个SCLK的下降沿采的数据,用了12个时钟,现在问,就是纯粹的对资料有疑问。

这个是时序图上看出的,您是说BUSY的高低电平都是由时钟CLK来控制,那BUSY在转换中的作用是什么?由谁来指示转换结束?还是说第8个CLK下降沿,busy上升为高电平,也就同时意为着转换结束(那完全不需要BUSY,只有第8个时钟CLK下降沿就意为着转换结束)?

谢谢您的回答。它的第9个时钟下降沿是转换好的数据的最高位啊,怎么会是第9个时钟下降沿采样呢?

谢谢您的解答,非常感谢,现在我们虽然采集数据完成了,但是对于资料还是有疑问。。

Hi

个人觉得是理解上的问题。

十二位的数据不会需要十三个SCLK,而在第十三个SCLK得到最后一位数据,意味着第一个SCLK没有数据,而波形明显可以看到这个SCLK是为了busy信号。

Hi

非常多的ADC都采用了数据转换完成(或者说数据预输出的)标识符,例如DRDY,或者Busy之类的信号,当控制芯片MCU/DSP等收到这个信号

后就知道ADC的数据已经转换完成,准备接收了。

这个并不能通过数SCLK的方式完成,在一个转换周期内,从CS置低,SCLK开始有信号,但是并不意味这控制芯片会在第一个SCLK时就发送DIN

命令,而datasheet定义完成DIN 8位输入即busy置高,在下一个SCLK下降沿(第九位)busy reset 低,标示可以接受数据了。

我觉得这个比数SCLK准确。

Hi

很多时候,可以结合调试的结果来理解datasheet , 这个被推荐。

谢谢您的解答,谢谢!

Hi

不客气。