四层PCB,顶层和底层运放对称布局的干扰问题

时间:10-02

整理:3721RD

点击:

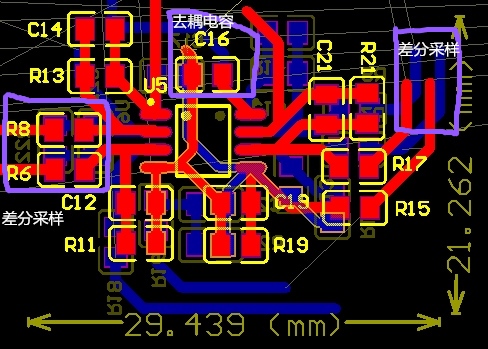

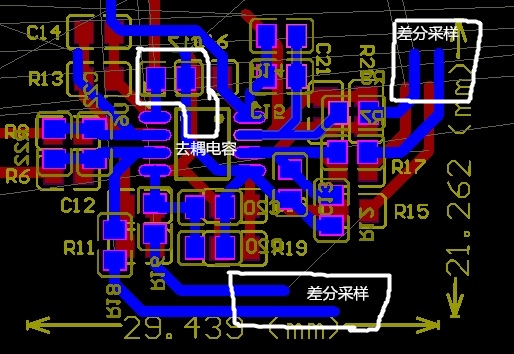

这是四层板,差分采样电路。运放采用AD8692ARZ(8引脚),差分采样信号,采样时间为10us。板子的面积有限,目前是上下两层各一个运放,不知道这样布局需不需要考虑高频干扰的问题。

如果考虑,是不是上下层两个运放,交错比较好一些。

信号的频率并不高, 电流也不大, 干扰就是有也比较弱

如果采用 4层板, 由大的地平面屏蔽, 那基本没有干扰了

当然, 你这样考虑还是有必要的.

AD8692ARZ这颗料不是TI的,不过一般PCB布局建议元器件都放在某一层。

嗯,这是普通的采样,调节器用的是OPA4228,这款是TI的

Top层,和Bottom层之间的物理连接只有一个+5v 和AGND。走线都是单面走线,没有过孔。地线是在中间层,大面积敷铜,指的是在Top和Bottom层,大面积敷铜吧。 非常感谢你的回复。

板子的面积比较小,就在背面放了一个采样电路

我个人觉得在空间合理的情况下,由于空间分布电磁场,还是分开处理好 ,方便采集信号,减少信号间串扰,提高抗干扰能力。