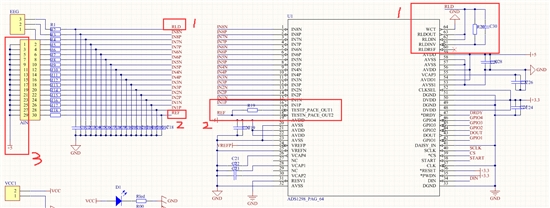

ADS1299引脚布局

问题1:如上图中方框1,右腿电路这样接法可以吗?其中BIASREF悬空了,这样可以吗?

问题2:如上图中方框2,因为ADS1299引脚兼容ADS1298,方框2中TEST_PACE1/2即SRB1和SRB2,这两个脚这样接法可以吗?

问题3:根据手册,不用的引脚要接去+5V工作电压,方框3的做法可行吗?

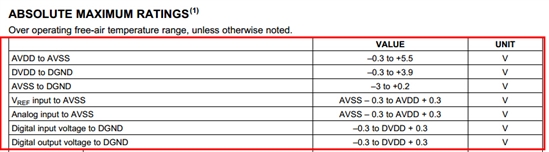

问题4:如下图,单电压供电时,每个单通道输入电压范围是(AVSS-0.3)至(AVDD+0.3)V,现在我AVDD接+5V,AVSS接AGND,这样供电方式可行吧?

问题5:如下图,单电压供电时,每个单通道输入电压范围是(AVSS-0.3)至(AVDD+0.3)V,现在我AVDD接+5V,AVSS接AGND,是不是说我IN8N和IN8P可以最小输入电压为-0.3V(对于AGND)?

谢谢各位!

1.从datasheet 的Figure52可以看出,BIASREF是内部bias amp的同相输入端,如果悬空的话是可以的,这样BIASREF_INT=(AVDD + AVSS) / 2。

那我的右腿电路如上图所接可以么?BIASREF悬空会影响右腿电路效果吗?谢谢

不用的引脚需要接到AVDD,所以接5V是没问题的。

4.单电源供电时,AVDD接5V,AGSS接AGND,没问题。

5. 表格中指的是芯片引脚所能承受的最大电压范围,也就是说当5V单电源供电时,输入引脚的的最小输入电压为 -0.3V,一般我们不推荐参考这个绝对值,而是参考数据手册的“RECOMMEND ELECTRICAL CHARACTERISTICS”,也就是在使用芯片的时候,通常输入电压不能低于AVDD,对于这款芯片来说,在Page20有个专门的对输入共模电压范围的详细介绍,可参考下。

通常输入电压不低于AVDD?

你是采用ADS1299 还是1298呢?我看你电路中是1298,这两款其实TI都有EVM板子,电路可以直接参考EVM user's guide中的电路。chapman ho

那我的右腿电路如上图所接可以么?BIASREF悬空会影响右腿电路效果吗?谢谢

不好意思,说错了,不低于AVSS,即不能低于0V。chapman ho

通常输入电压不低于AVDD?

我是采用ADS1299,因为TI网站找不到ADS1299的CAD文件,然而1299手册又说引脚封装兼容1298,所以我就拿了1298来画图。可以把?

问题1中,右腿电路可以那样接法吗?BIASREF悬空会影响右腿电路效果吗?谢谢

恩,二者引脚兼容的,不会影响的,RLDREF悬空的话,就和1299的BIASREF悬空一样,都是采用内部偏置为(AVDD + AVSS)/2的电压,只是通过配置内部寄存器RLDREF_INT=1将RLDREF_INT开关打开,RLDREF_INT反开关闭合。chapman ho

我是采用ADS1299,因为TI网站找不到ADS1299的CAD文件,然而1299手册又说引脚封装兼容1298,所以我就拿了1298来画图。可以把?

问题1中,右腿电路可以那样接法吗?BIASREF悬空会影响右腿电路效果吗?谢谢

好的谢谢您!

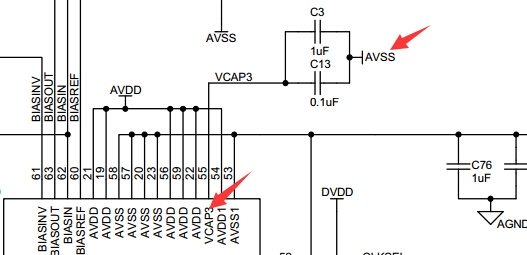

Hello,Kailyn.

ADS1299EVM电路图中,这个VCAP3接了电容后接AVSS。假如我是双电源(AVDD接+2.5V,AVSS接-2.5V)这个VCAP3这个位置还是接电容后接AVSS(-2.5V)还是接AGND?其他VCAP1/2/4也有这个。

THANK YOU!