使用VCS进行网表仿真的的困惑

时间:10-02

整理:3721RD

点击:

1.工具:VCSNX1103SP1。2.对象:网表,无时序,TMAX自动产生的testbench。

3.问题:某个寄存器模型的输出有误,不可理解。

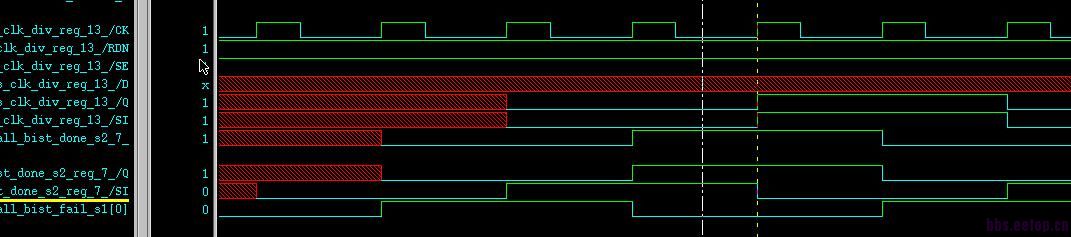

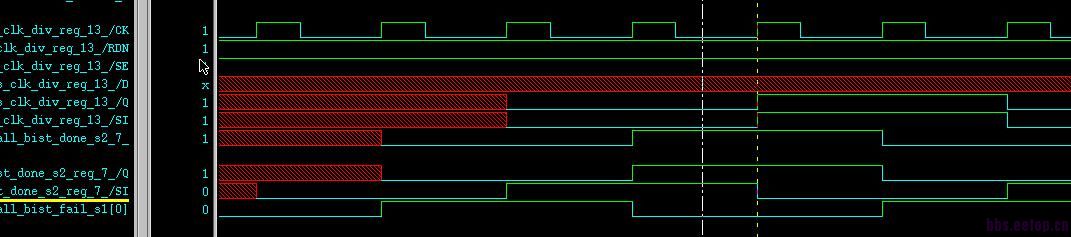

4.现象:在SCAN使能的模式下,该寄存器(图中的reg_13)的CLK,SI,Q三个信号同时发生翻转。这个寄存器是有SE端的寄存器,他的前一级寄存器是个移位寄存器,输入是done_s2_7,输出是reg13_si。输入链路与这个看似完全相同的寄存器reg_7,得到的结果却是不一样的。输入与此类似的是reg_7的寄存器,但是该寄存器的行为正确。这两个寄存器使用同样的仿真模型,只是不同的例化而已。

3.问题:某个寄存器模型的输出有误,不可理解。

4.现象:在SCAN使能的模式下,该寄存器(图中的reg_13)的CLK,SI,Q三个信号同时发生翻转。这个寄存器是有SE端的寄存器,他的前一级寄存器是个移位寄存器,输入是done_s2_7,输出是reg13_si。输入链路与这个看似完全相同的寄存器reg_7,得到的结果却是不一样的。输入与此类似的是reg_7的寄存器,但是该寄存器的行为正确。这两个寄存器使用同样的仿真模型,只是不同的例化而已。

用$vcdplusdeltacycleon看看各事件的顺序是否有差异。不过你得换DVE看波形了

学习了。今天按照nativeda的提示,终于发现问题了。驱动reg_13 SI的时钟和驱动reg_13的时钟不是同一个时钟。由于不加时延,所以两个时钟看起来是一样的,其实两个时钟不是同一个,逻辑上有因果,先后关系,实际上有时差。驱动reg_13的时钟是从驱动SI的那个寄存器的时钟衍生来的。 总结,对于后端提取的网表,必须加时延文件,再进行仿真。

总结,对于后端提取的网表,必须加时延文件,再进行仿真

后仿前会先用网表文件做门仿,不带时序信息SDF文件的。门仿该怎么解决这个问题?

现在很少会做不带SDF的门仿了吧?如果确实需要,就用+delay_mode_zero吧

你说的“门仿”就是网表仿真吧,这个网表是综合工具输出的网表,他和RTL是完全一致的,所以仿真也和RTL是一样的,只是多了一些元件库文件而已吧。

是的。但是总会有人提出让我难以拒绝的,特别的要求。

”完全一致“是需要验证的,但不是一定要用动态仿真来验证

kkkkkkkkkkkkkk