UVM connect 出错?

时间:10-02

整理:3721RD

点击:

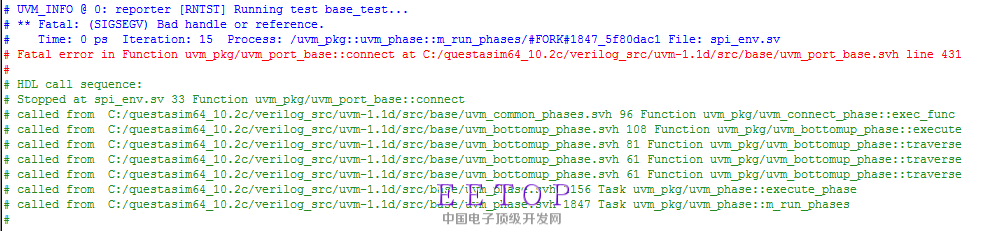

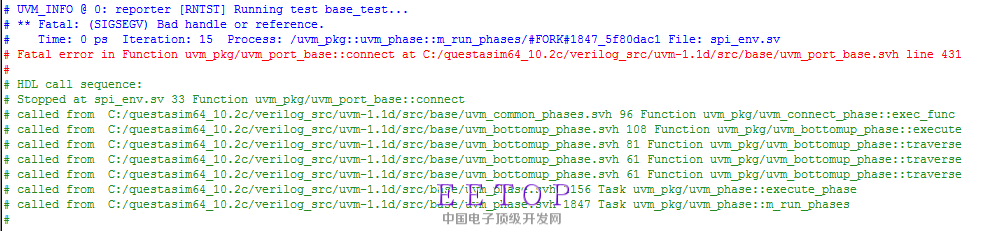

Fatal error in Function uvm_pkg/uvm_port_base::connect at C:/questasim64_10.2c/verilog_src/uvm-1.1d/src/base/uvm_port_base.svh line 431

没查到这个错误出在哪,代码参考了张强的代码

程序:

class SPI_env extends uvm_env;

`uvm_component_utils(SPI_env);

SPI_agent

i_agt, o_agt;

SPI_model

mdl;

SPI_scoreboard scb;

uvm_tlm_analysis_fifo #(SPI_transaction) agt_scb_fifo;

uvm_tlm_analysis_fifo #(SPI_transaction) agt_mdl_fifo;

uvm_tlm_analysis_fifo #(SPI_transaction) mdl_scb_fifo;

function new(string name = "SPI_env", uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

i_agt = SPI_agent::type_id::create("i_agt", this);

o_agt = SPI_agent::type_id::create("o_agt", this);

i_agt.is_active = UVM_ACTIVE;

o_agt.is_active = UVM_PASSIVE;

mdl = SPI_model::type_id::create("mdl",this);

scb = SPI_scoreboard::type_id::create("scb", this);

agt_mdl_fifo = new("agt_mdl_fifo", this);

agt_scb_fifo = new("agt_scb_fifo", this);

mdl_scb_fifo = new("mdl_scb_fifo", this);

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

i_agt.ap.connect(agt_mdl_fifo.analysis_export);//报错在这行

mdl.port.connect(agt_mdl_fifo.blocking_get_export);

mdl.ap.connect(mdl_scb_fifo.analysis_export);

scb.exp_port.connect(mdl_scb_fifo.blocking_get_export);

scb.act_port.connect(agt_scb_fifo.blocking_get_export);

o_agt.ap.connect(agt_scb_fifo.analysis_export);

endfunction

endclass

就对了

没查到这个错误出在哪,代码参考了张强的代码

程序:

class SPI_env extends uvm_env;

`uvm_component_utils(SPI_env);

SPI_agent

i_agt, o_agt;

SPI_model

mdl;

SPI_scoreboard scb;

uvm_tlm_analysis_fifo #(SPI_transaction) agt_scb_fifo;

uvm_tlm_analysis_fifo #(SPI_transaction) agt_mdl_fifo;

uvm_tlm_analysis_fifo #(SPI_transaction) mdl_scb_fifo;

function new(string name = "SPI_env", uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

i_agt = SPI_agent::type_id::create("i_agt", this);

o_agt = SPI_agent::type_id::create("o_agt", this);

i_agt.is_active = UVM_ACTIVE;

o_agt.is_active = UVM_PASSIVE;

mdl = SPI_model::type_id::create("mdl",this);

scb = SPI_scoreboard::type_id::create("scb", this);

agt_mdl_fifo = new("agt_mdl_fifo", this);

agt_scb_fifo = new("agt_scb_fifo", this);

mdl_scb_fifo = new("mdl_scb_fifo", this);

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

i_agt.ap.connect(agt_mdl_fifo.analysis_export);//报错在这行

mdl.port.connect(agt_mdl_fifo.blocking_get_export);

mdl.ap.connect(mdl_scb_fifo.analysis_export);

scb.exp_port.connect(mdl_scb_fifo.blocking_get_export);

scb.act_port.connect(agt_scb_fifo.blocking_get_export);

o_agt.ap.connect(agt_scb_fifo.analysis_export);

endfunction

endclass

你 i_agt o_agt 里的ap 应该跟monitor连的吧 两个montior 采集的trans类型一样么?

一句话点醒梦中人!我突然意识到bug可能出在哪了!谢谢!

修复成功!谢谢回复!果然自己看自己的代码会有盲区。在i_agt里我省略了mon,应该直接在drv里把trans驱动到ap上,但是在drv里忘记初始化一个ap导致i_agt的ap是悬空的了。

agent的connect改成

- function void connect_phase(uvm_phase phase);

- super.connect_phase(phase);

- if(is_active == UVM_ACTIVE)begin

- drv.seq_item_port.connect(sqr.seq_item_export);

- ap = drv.ap;

- end else

- ap = mon.ap;

- endfunction

就对了