关于用Testbench搭建验证环境的问题!?

是不是将DUT(10个小模块)、BFM(对应着RTL有10个小模块)loading到Modelsim进行编译,然后将Testbench loading到Modelsim中编译,最后添加信号开始仿真,再看波形呢?求解!

你是说的SV还是纯粹的hdl?应该需要在仿真的时候指定你的testcase。最好是把你的具体环境描述一下。

单纯的verilog写的啊,要用Modelsim进行仿真,整个project有10个RTL模块,对应着10个BFM模块,还有testbench

和testcase,仿真的步骤是怎样的呢?

定义一个最顶层的test-top,把所有的东西都包括起来,然后做连接,这个test_top是一个无端口的module。或者你的testcase就是这个test_top,里面应该包含了testbench,而testbench就是各种bfm和dut的连接关系吧。是不是这样?

如果你已经按4楼说的做好了,那么,你建立一个Projec.f的文件,里面把你所有的文件,包括RTL代码和BFM和验证顶层都放进去,把"-f Project.f"加载进去就OK了,

好像不是的,我的testcase里面是:

INITIAL;

$readmemh("../data/v5.txt",mem);

ch_msg = $fopen("../log/tc_v5.txt");

vector_num = 10;

for(i = 0;i < vector_num;i = i + 1)begin

CLK_IN(mem[19:4],mem[2],mem[1],mem[0]);

end

STOP(4000);

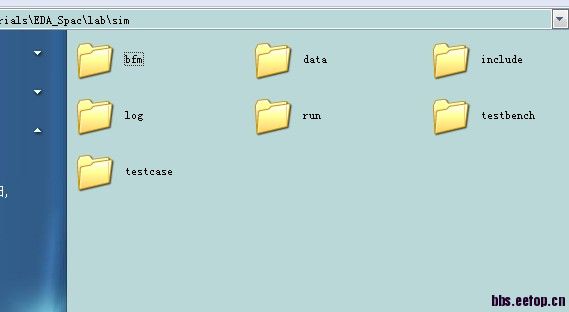

这样的code。 怎么回事呢?这是project的文件列表截图:

哎,你只截了TESTCASE里面最没用的这段,我想看是你的是TESTCASE定义成了PROGRAM还是MODULE,定义成什么名字,比如定义成这样:

program test;

xxx;

xxx;

initial begin

end

endprogram

这样的话,肯定还会有一个文件把你的test和DUT顶层包起来,

那个文件才是最高的顶层。

回到你最开始的问题,我认为,你只要把所有的文件都加载进去,就应该是OK了,

因为看你的截图像是一个DEMO,直接就可以用的。

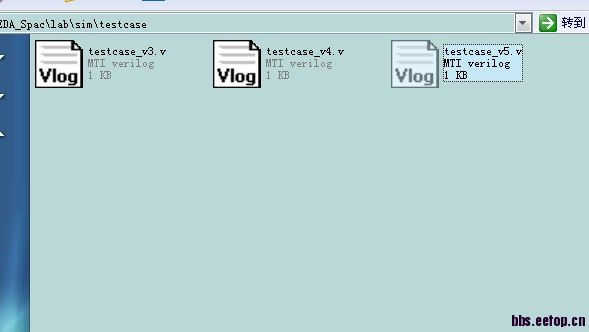

有三个testcase文件第二个是:

INITIAL;

$readmemh("../data/v5.txt",mem);

ch_msg = $fopen("../log/tc_v5.txt");

vector_num = 10;

for(i = 0;i < vector_num;i = i + 1)begin

CLK_IN(mem[19:4],mem[2],mem[1],mem[0]);

end

STOP(4000);

第三个是:

INITIAL;//开始count1为000,即时间正常显示

ch_msg = $fopen("../log/tc_v4.txt");

CLK_IN(10000,1,0,0);//count1变为001,即日期设置,且高两位闪烁

CLK_IN(4,0,0,0);

CLK_IN(10000,1,0,0);//count1变为010,即时间设置,且高两位闪烁

CLK_IN(4,0,0,0);

CLK_IN(10000,1,0,0);//count1变为011,即秒表设置,秒表开始记时

CLK_IN(4,0,0,0);

CLK_IN(10000,1,0,0);//count1变为100,即闹钟设置,且高两位闪烁,低两位灭

CLK_IN(4,0,0,0);

CLK_IN(10000,1,0,0);//count1变为000,即时间显示,跑完一个循环

CLK_IN(4,0,0,0);

STOP(1000);

顶!

我顶!

每个testcase就这些?没有module定义和信号定义?你最好先把文件夹下所带的所有文件都理清楚是干什么用的,不要没头苍蝇一样的乱撞,一般肯定应该是有一个最顶层的文件。加载到modelsim之类的工具以后仿真运行那个文件即可。

我顶!

居然还是 下不完 啊

帮你顶

你那个RTL文件夹里的文件是连接在一起的还是分散的模块啊?如果是可连接在一起的应该就是4楼说的那样,把RTL封装成一个模块,然后用interface把BFM连接上,定义agent,driver,monitor什么的。

顶!