uvm 芯片中存在多个模块级联的情况,请问级联内部的信号怎么监测的?

时间:10-02

整理:3721RD

点击:

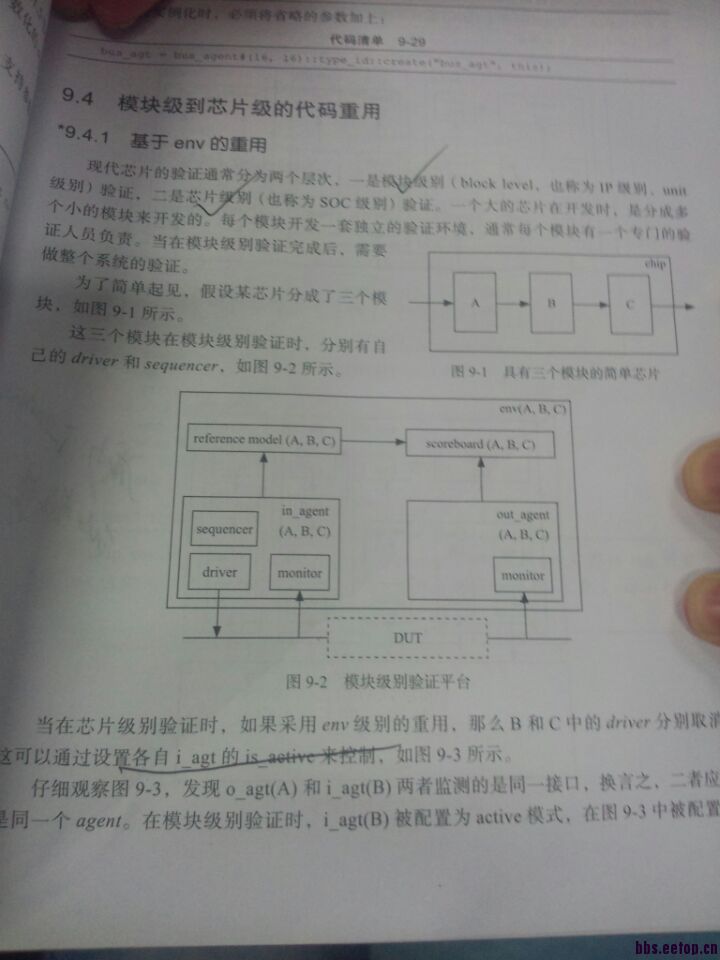

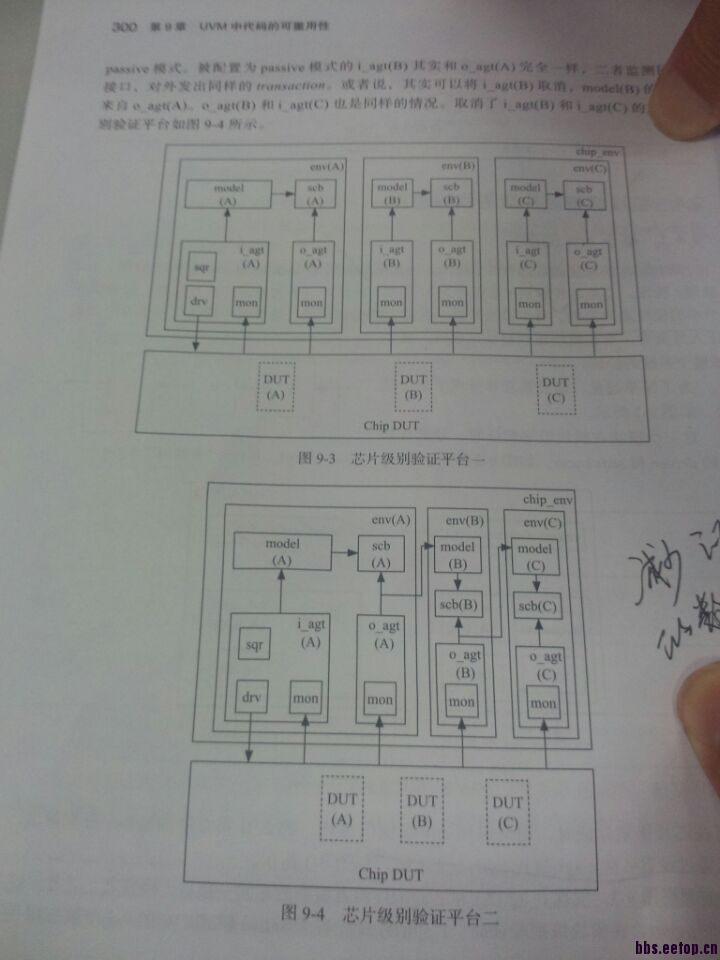

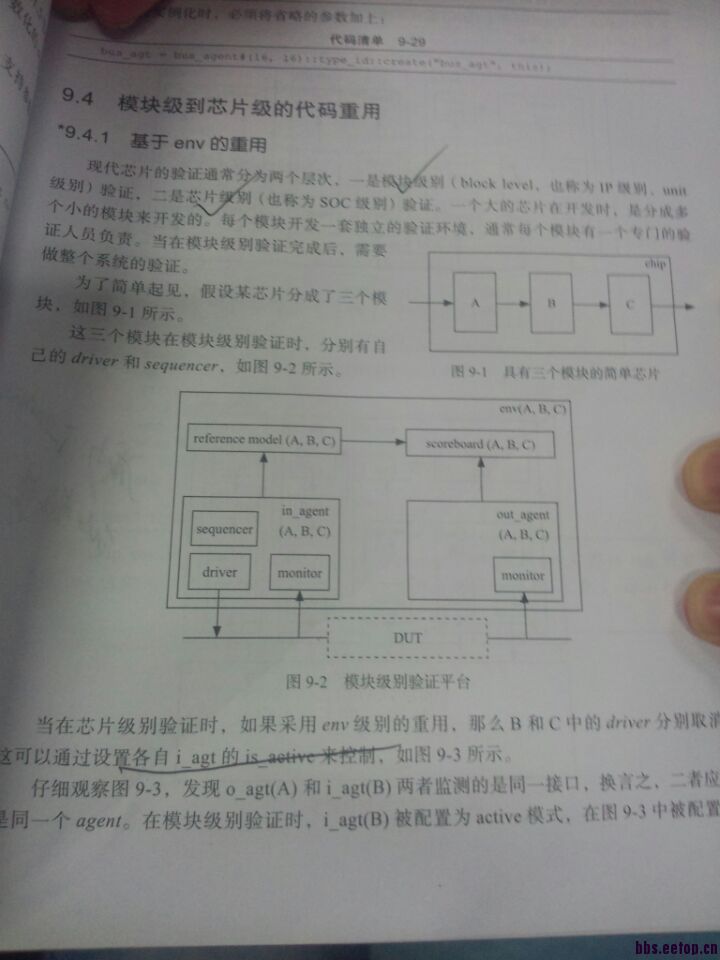

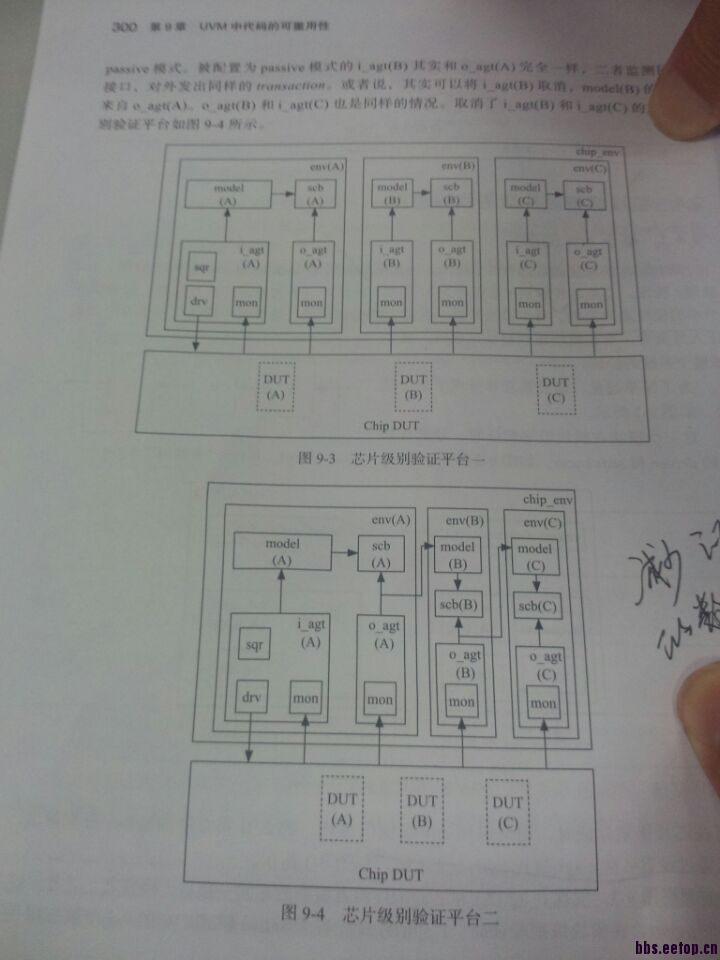

各位大神,大家好,最近在搭建UVM系统级验证平台。现在准备将模块级的ENV进行重用,内部模块的driver,sequencer,自然是不用了,但是monitor要怎么连接呢?我不清楚内部模块的信号是怎么传递给monitor的?

刚买了本张强出本的UVM实战,讲的很好,但是这块确实不明白,现在附上图,拍的不是很清晰,

刚买了本张强出本的UVM实战,讲的很好,但是这块确实不明白,现在附上图,拍的不是很清晰,

通过interface

问题是级联内部端口的信号不在顶层,interface要怎么连接呢?

使用assign

assgin block1_if.signal = test_top.chip_inst.block1_inst.signal

我试试看,谢谢大神,如果级联的模块比较多的话,那岂不是要用很多assign语句?

是的,模块越多意味着这块芯片越复杂,必然会有更多的接口,更多的assign语句。

我记得好像是用xmr把design内部的信号spy到if上