高手进,芯片ESD电路问题!?

在设计一块DC-DC芯片时,芯片的所有引出PIN脚都需要接ESD电路么?还是说只要模拟部分的pin脚需要连ESD电路,而数字部分不需要?另外,如果把外部开关的驱动管做在了芯片内部,那么芯片引出的驱动信号pin脚(应该属于功率级了吧)需要连ESD电路么?还有,如果芯片的一个引出pin脚连接的是电容,那么这个引出pin脚需要连ESD电路么?因为我在实际仿真的时候,发现,如果在这类pin脚连ESD电路的话,ESD电路会引入一定的寄生电容,这样的话,我实际的仿真结果和理论上的结果就会存在一定的偏差了,。那这个时候ESD该怎么接呢?或者说选择怎么样的ESD电路呢?

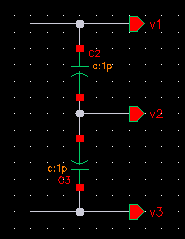

输出pin脚 V1,V2,V3的ESD怎么设计?要求寄生电容很小?

输出pin脚 V1,V2,V3的ESD怎么设计?要求寄生电容很小?

ESD是一个比较复杂的topic,建议小编找些资料先看看。

即使上面这些问题你都得到了答案,最后也仍然可能fail。

每一个pin都要ESD保护(包括自保护),对受电容影响的电路一定要带入ESD进行仿真,寄生电容对电路影响大就不能用foundry提供的常规ESD结构,可以上个电路图具体讨论。

一般来说除了POWER和GROUND(有时候也需要加ESD)外的所有PIN都需要加ESD,只是防护级别根据实际而定,起码你得保证你的芯片要robust,然后才是性能多好

学习了

顶上去,哈哈

如果这三个pin是给analog or digital block 提供电压(要求寄生电容很小吗?),输出pin只是为了方便测试的话,就按照power pin and IO pin的ESD来做(power clamp with GGMOS)。看你图 也不像这样做

与pin连接的电路具体点(可以把你现在考虑的ESD protection方案也带上),三个pin,两个电容很难看明白。

7# zhukh

是的。这三个pin都是analog电路的输出pin,我只是为了方便测试用的,,,你说的power pin and IO pin的ESD的电路 具体是怎么样的? 你能给个图或者资料么?(power clamp with GGMOS)。

都是analog电路的输出pin, 仅当输出? 如果是,就用像其他pin一样,用Gate grounded NMOS and gate to vdd PMOS就可以了。只是输出管本身也可以做成自保护的ESD管。

现在不方便帖图。

9# zhukh

你说的是GGMOS或者GCMOS? 那是这样的话, 在V1,V2端 不就引入了较大的寄生电容了么? 因为V1,V2脚本身链接的就是pf级的电容!?这里只对V2脚进行ESD保护,V1,V3不用,可以么?

Q:你说的是GGMOS或者GCMOS?

A: for IO, i do not recommend you to use gate coupled MOS as ESD protection.

Q: 你说的是GGMOS或者GCMOS?

A: if you want to reduce the parasitic capacitance, use pure diode.

Q: V1,V3不用,可以么?

A: yes, if you don't care about V1 and V3,and the chip will function well even ifV1 and V3 are damaged by ESD stress.

11# zhukh

PIN脚被ESD击穿的话,不影响你的芯片内部电路么?

你说的 栅极耦合MOS 结构是怎么样的?

我知道,GGMOS是G,S短接!

so, why dont you add ESD protection? Every pin need ESD protection!

GCNMOS: C between Drain and Gate, R between Gate and Source.

13# zhukh

如果用两个二极管加一个电阻来做ESD保护的话,那这两个二极管要用多大的?我现在用的CMOS工艺里,有PDIO和NDIO两种,但是面积选择多大的为好,还有这与pin串联的电阻要多大为好!?谢谢

也不一定要加电阻。什么工艺,我没用过工艺提供的PDIO和NDIO二极管。自己画的,1.5um*20um, 3 finger is enough for 0.18um CMOS process. if you want to add resisitor, 100~200ohm is usually used.

15# zhukh

TSMC .35 工艺,PDIO是做在n井里面的,NDIO是做在衬底上的!?

我想PDIO应该是P+/Nwell diode, NDIO是N+/Pwell diode

for IO to GND, use N+/Pwell diode

for IO to VDD, use P+/Nwell diode.

or you can use P+/Nwell diode for both.

17# zhukh

用的是单井工艺,N井工艺!~ESD保护用两个二极管,一个连VDD,一个连GND,两个二极管之间是输出PIN?是这样连么? 但是这个时候,二极管的尺寸(宽,长选多少合适呢?)

it‘s ok that Pin 2 Pin ESD is Pass

学习了。

19# kelvinsz

什么意思?你指的是,只对PIN2进行ESD保护就OK了么?或者说只对PIN2

进行ESD保护,不对PIN1和PIN3进行ESD保护也是可以的么?

he said there is no potential ESD failure in terms of pin to pin zapping combination due to capacitance between two pins as you illustrated in the schematic. but you have more than three pins, right ?

帮顶帮顶。

帮顶帮顶

初学,还不太明白,问一下tsmc工艺库中有没有不接地的二极管?