我觉得UVM1.1中的官方给的例子代码中有缺陷,请高手指教。

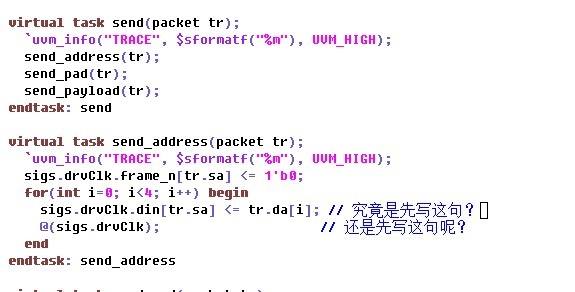

上图是官方代码

描述如下:官方代码是先写了sigs.drvClk.din[tr.sa]<=tr.da 再写 @(sigs.drvClk);也就是等待时钟写在后面。而官方代码没有出现问题,是因为碰巧在执行send函数前 别的操作有时钟上升沿到来,也就是说,官方代码没有出错,是因为运行时碰巧是如下的情况。也就是sigs.drvClk.din[tr.sa]<=tr.da之前有了若干个@(sigs.drvClk)。要是让send第一时间就工作,一个数据就丢失了,我感觉官方的代码是碰巧没有出问题而已。

我的结论:我认为同步驱动数据时应该先写@(sigs.drvClk),也就是如下所示:

请大家指教!官方代码按理说应该没有缺陷啊。纠结了很多天,但是我还是想知道官方这种代码到底有没有问题。大家平时在同步驱动数据时是怎么做的呢? 请指教~谢谢~

请大家指教!官方代码按理说应该没有缺陷啊。纠结了很多天,但是我还是想知道官方这种代码到底有没有问题。大家平时在同步驱动数据时是怎么做的呢? 请指教~谢谢~

初始化时丢几个数据没什么大不了。

synopsys 竟然会出这样的示范代码..............

向DUT驱动数据时采用你给的方式,而从接口总线接收数据时,类似上述官方所给代码,相同的问题,在for或foreahc循环前会比预期的多一个时钟周期。

sigs.drvClk.din[tr.sa]<=tr.da

用了clocking block,本来就是同步驱动的。数据是在时钟沿之后被驱动到信号上

同意5#, 代码中即使没有显式等待时钟沿,数据也会等到下一个有效时钟沿才赋值。

没有问题啊。这个你要看看DUT是什么行为才行,有些是先等一个时钟,有些是出了数据要打一拍。

怎么会有错呢?

- program test(router_io.TEST io);

- initial begin

- io.drvClk.din<=16'h2;

- @(io.drvClk);//假如这句没有

- io.drvClk.din<=16'h4;

- @(io.drvClk);//假如这句没有

- io.drvClk.din<=16'h7;

- @(io.drvClk);//假如这句没有

- io.drvClk.din<=16'h9;

- @(io.drvClk);//假如这句没有

- #50 $finish;

- end

- endprogram: test

但是 要是去掉上面代码中的@(io.drvClk);那么只有最后io.drvClk.din<=16'h9;执行了,其余的没有机会驱动数据。我在这一块内容纠结好久了。 真想搞得清楚点,要不我自己写的代码 都不知道到底怎么运行。求解啊~谢谢大家~

PS :所以6楼“代码中即使没有显式等待时钟沿,数据也会等到下一个有效时钟沿才赋值。”应该不成立吧?

你的代码中,没有@(io.drvClk)的话,仿真一开始,所有的赋值都会在第一个时钟沿后起效,结果当然是最后一句覆盖前面所有的。

要推动仿真时间前进,肯定要靠@(io.drvClk)。

clokcing block的作用就是,在bench中,在一个时钟上升沿之前对信号作了驱动,该值只有等到时钟上升沿才到达DUT

在用vcs仿真的时候,数据一定会在时钟后给出的。

io.drvClk.din<=16'h2;

04.@(io.drvClk);

06.io.drvClk.din<=16'h4;

07.@(io.drvClk);//假如这句没有

io.drvClk.din<=16'h2;你应该是拿不到这个数据的

这个例子从哪来的,能不能给个附件

要是像你那么理解去改变顺序的话仿真会死掉的,这个顺序是对的,不信你自己试试

好好看看时钟块的概念

都在UVM了,落后了!

您好,能把这个官方的实例代码传一份给我妈

说的很对,学习了...

的确有问题。

小编,你好,请问官方代码爱哪里有下载呢?抑或是能否传我一份,多谢了。guikunkun@126.com