ICC抽取sdf文件后用NC-verilog仿真,有很多timing violation,导致数据不能正常存储

我用ICC导出sdf文件的命令是write_sdf ./final1.sdf

在ICC里面仔细查过了,没有timing violation。求教大神有没有知道可能是什么原因啊?求指导!

还有十几天就要流片了,着急啊。每天这样熬着精神快奔溃了。

你先从两个方面去排查一下

1.看看testbench种输入的激励,时序上对不对。

2.时序约束file中是不是对应该约束的时钟都做了约束,比如一些false path

这两个都没有问题后,那就要根据timing violation的information一个个去查了

你好,请问如何确定是否得到约束了呢?小弟刚刚入门,很多还不懂

timing violation问题:你可以先分析下是不是这个时序错误会导致设计fail,如果只是假错,在Nc_verilog选项中,notiming check选项,就可以了

你好,我在ICC上检查时序是没有问题的,但是在仿真时会报错,提示有时序违约。如果不checktiming的话,数据是错误的,看来真的不是假错了。不过在ICC上查对应路径的slack很充足啊,没有违约的。

这样的情况的话可能的问题:1.查看下你输入的激励,看是否由不合理的激励引起接口上的violation;

2.如果你是多个apr综合后拼接到一起仿真的话,你可能不止要查检当前的icc时序,要联通前面的时序,一起做接口时序查检;

3.如果你仿真时候连着真正的模拟电路进行仿真的话,你可能还要把模拟电路的coupling影响考虑在内。

希望对你有帮助@

个人感觉NCSIM对SDF的支持性不如VCS做的好。建议使用VCS做后仿真!

你好,感谢您的回答!我现在用NCverilog和VCS仿真都出现了TimingViolation,我昨天在NC仿的时候加了+notimingcheck命令,结果就没有Violation了(因为没有检查时序),不过从结果上来看还是基本可以实现的,和综合后仿真的结果是一样的。请问这样子可以了吗?要做更详尽的测试与仿真已经没有时间了。

你使用+NOTIMINGCHECKS这个仿真选项之后,相当于不检查时序,当然没有timing violation。

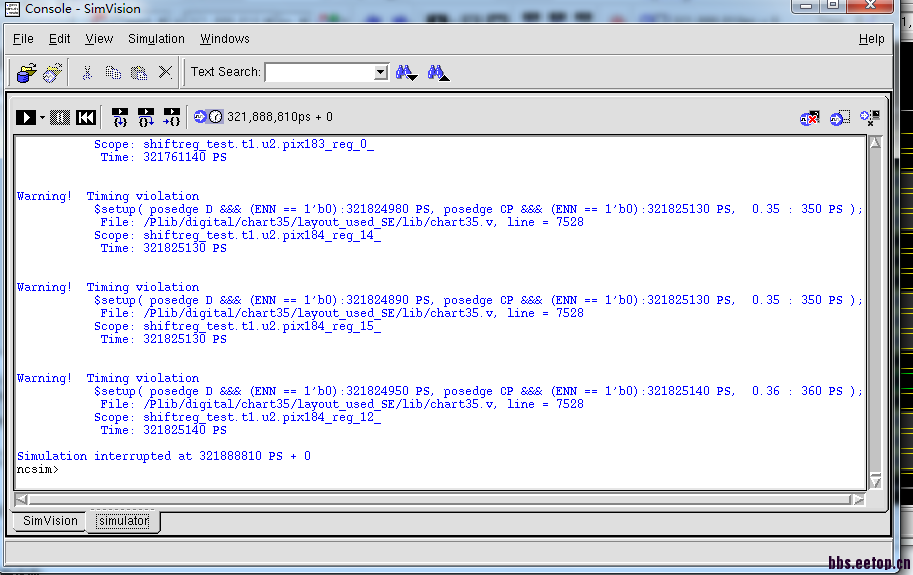

我刚才看了你的截图,是有setup 的timing violation。不知道你是进行哪个Corner的仿真?

我觉得你可以从以下几个方面来着手:

1,如果马上要流片,时间不足,那么,首先进行Formality形式验证,保证网表和rtl功能一致性;

2,马上进行STA分析,使用OCV来进行STA分析,对SDC约束文件,一定要有丰富经验的人员来保证,同时和设计人员来逐条查看其设置是否合理;

3,如果以上两步均正确,那么,如果你的设计很少采用异步逻辑的话,基本可以保证95%的正确性;

4,同时继续查找后仿真的问题,我看了下是setup 的timing violation,故你先降频来运行仿真。

比如你原来仿真主时钟是30MHz,那么先25MHz的情况下来运行仿真,看有没有timing violation。

5,另外,严格仔细的查找你的后仿真的仿真参数选项。最好你把你仿真的参数选项,以及你的$sdf_annotate任务全部贴在下面,让我们都看看,检查下。

供你参考。

10#说的正确。