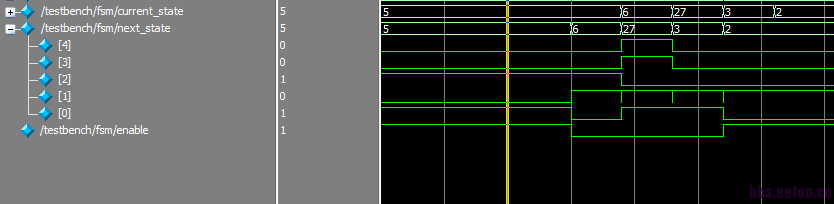

状态机 毛刺

代码为always @(current_state or in)

begin

case(current_state)

s1:

if (in == ...)

next_state = s2;

....

default:

next_state = s1;

....

状态为格雷编码

请问毛刺的产生原因以及如何消除?

没太仔细看...说说我的看法,

如果是前仿真,看一下in 信号是不是在时钟沿变化了。

如果是后仿真,current_state各个位会有延迟这是正常现象。

前仿 对的 in信号的确是在时钟沿变化的。

请问,有什么解决方法么?

写testbench的时候,让in别在时钟沿变化,看看结果对不对

可是。in的确是在时钟上升沿变化 啊。

其实我觉得这个现象对你的状态机没有影响吧,在下个时钟沿来之前,next_state已经稳定了,那状态的转换也不会有什么问题。

如果你的後級電路倚靠 state machine 的 state value, 那麼 output 一定也有 glitch, 將此訊號透過相同的 CLK latch 一次再輸出即可.

纯支持,不太懂

纯支持,不太懂

try using non-blocking assignment

在testbench中对你的in的信号相对clock都做#1的延迟

如果IN有毛刺,那么Next_state就会有毛刺。可以用时钟锁一拍IN。此外IN和当前状态不应该“同时”发生变化。

问题解决了吗?

若不想改设计,就加个delay cel 或一下就行了。或者in信号先过一个触发器。

使用verilog写状态机,记得好像是可以通过调整触发时间消除毛刺,具体不是太清楚,不过这应该不会影响你的仿真结果,只要不出现竞争冒险,一般不许要理会!

使用 one hot编码

状态机的输入应该是前级capture的,不会在时钟边沿到来的吧,不满足hold time了

这个和setup time ,hold time没有关系,要看你的in激励是怎么加的(是直接#XX,还是由clock触发?)。

还要看仿真器的调度机制。

最简单的做法是不要让IN和clock同沿变化,加个delay 就好。

实际状态机的电路里面输入信号是不可能在时钟边沿到来的。我说的这个没错么。意思就是小编的这个激励信号没加正确

这是前仿真,肯定是状态机写的不对。你确定你是三段的方式吗?每次状态都是时钟沿后面变化?