模块间的时钟约束问题

时间:10-02

整理:3721RD

点击:

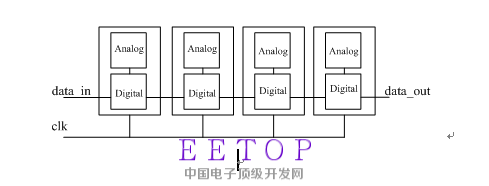

背景:有16个这样的模块,每个模块都是模拟+数字组合,数据串行进入,串行输出,中间模块首尾相连,上一个模块的输出接下一个模块的输入。

模块级联示意图

问题:现在采用模拟的方式,手动插入时钟树,每个模块的时钟应该满足一个什么样的要求?

假设每个模块需要5ns就可以输出有效数据,那么clock source 到相邻的两个模块的CLK端的latency要小于5ns即可?

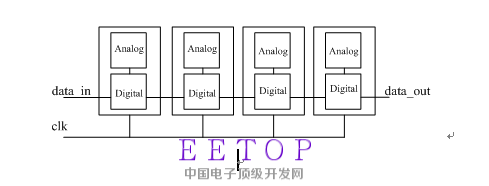

模块级联示意图

问题:现在采用模拟的方式,手动插入时钟树,每个模块的时钟应该满足一个什么样的要求?

假设每个模块需要5ns就可以输出有效数据,那么clock source 到相邻的两个模块的CLK端的latency要小于5ns即可?

自己顶一个

具体latency我不知道怎么算,但是应该先判断是否属于multi-cycle路径,那也许就可以有比较大的裕量了。

一语惊醒梦中人啊,很有道理,我明白了,谢谢

如果不是多周期路径的话,是不是前一个模块输出数据时,后一个模块必须可以采样到就可以保证正确了,即二者的latency小于一个时钟周期