复数乘法器没有输出,不知道原因的我眼泪掉下来

时间:10-02

整理:3721RD

点击:

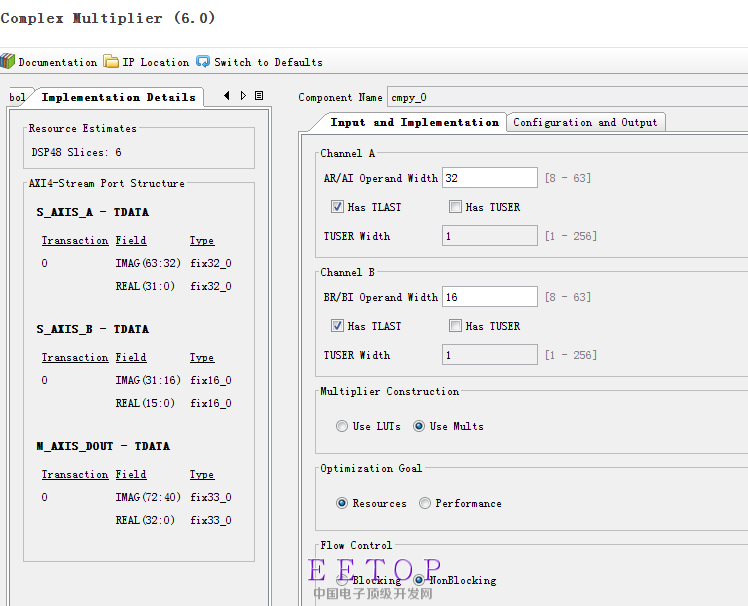

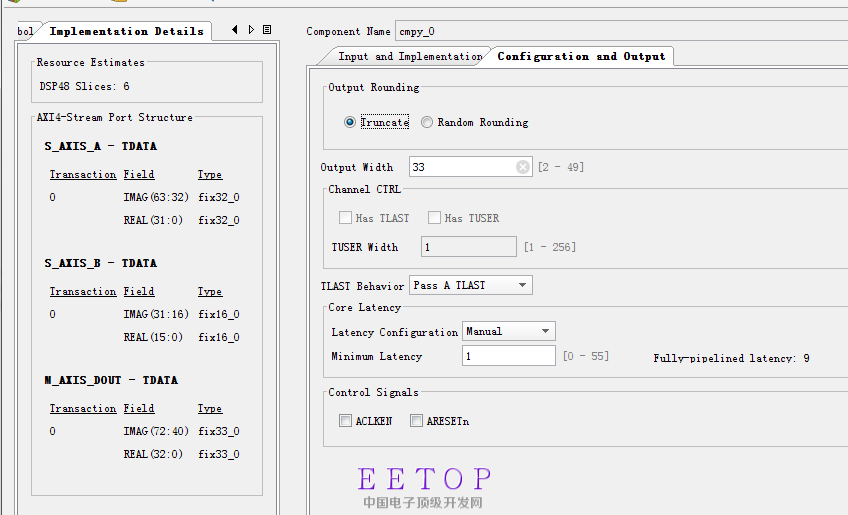

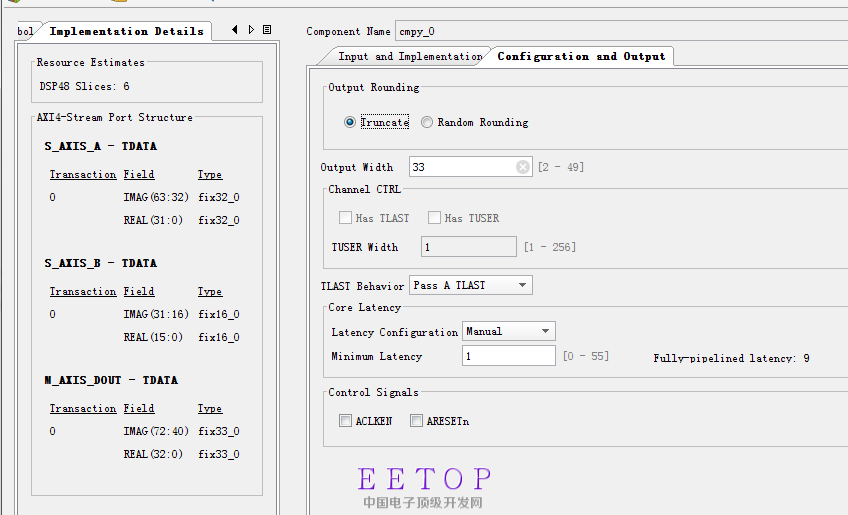

我的输出延时直接设置成1个clock cycle

A输入64位,32位实部,32位虚部。

B输入32位,16位实部,16位虚部。

输出共80位,实部,虚部都是33位。

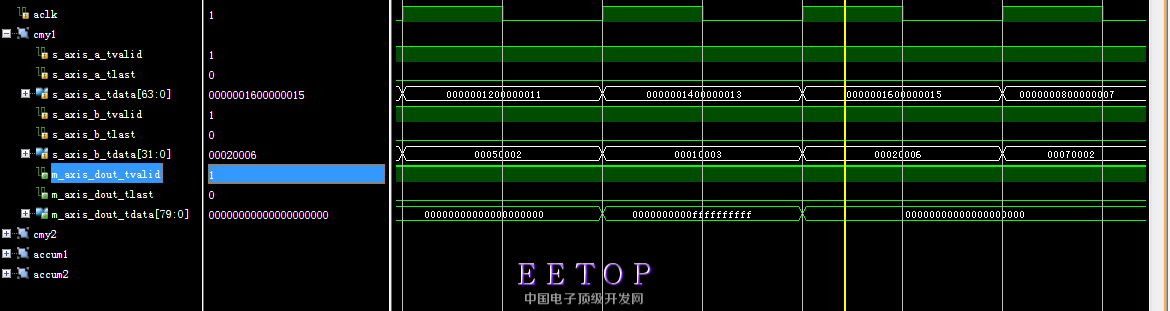

这都没有问题,可是为什么没有输出呢。

是什么原因呢,我觉得设置也没有问题啊。

高人给指点一下吧。

A输入64位,32位实部,32位虚部。

B输入32位,16位实部,16位虚部。

输出共80位,实部,虚部都是33位。

这都没有问题,可是为什么没有输出呢。

是什么原因呢,我觉得设置也没有问题啊。

高人给指点一下吧。

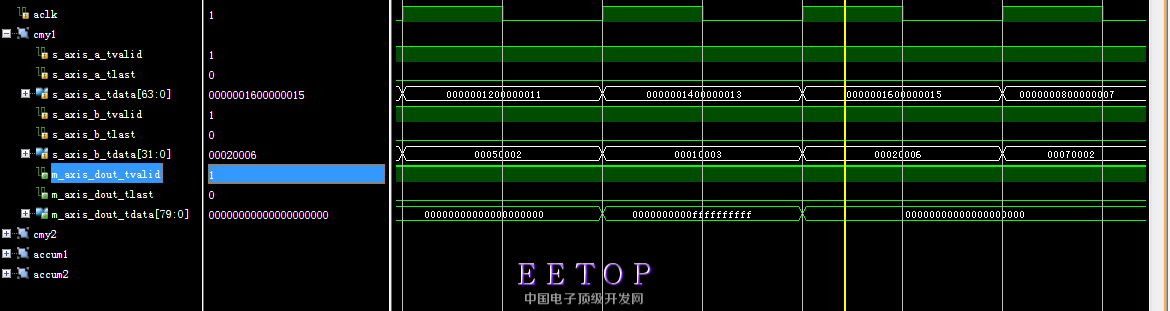

是不是跟仿真数据有关系,这些输入复数相乘结果可能就是这个吧,你可以换一些确定复数相乘结果不为0的输入数据试试

首先谢谢您的回复和建议。

经过我的进一步分析,已经找出了原因。

输入A的实部,虚部都是32位,输入B的实部虚部都是16位,那么输出应该是多少位呢?36+16+1=49位,即输出位的实部虚部都是49位才能完全显示结果,不至于截位。而我设置的输出位是33位,那么也就是说低49位的低16位被截掉了,而我给的输入数值又非常小,远小于65536,直接被截掉了。

把输出设置成49位,没问题,结果是对的。

00000也是输出,,,,