器件内部时钟问题?

时间:10-02

整理:3721RD

点击:

[这个贴子最后由showting在 2005/03/01 08:01pm 第 2 次编辑]

(图片不清可点击发大)

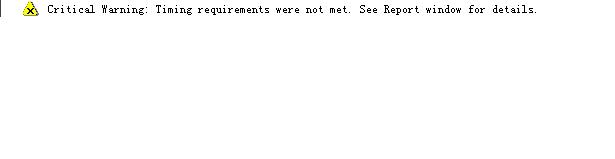

这是我作仿真时消息框内的一条警告。后来我换用了stratix系列器件作仿真,还是有这条消息。我怀疑是内部的连线较多而且信号的速度较快对布线有影响,就是说两个模块之间的连线很多,对于用什么样的可编程器件在这两个模块之间都不好布线,所以改过器件后还是出现同样的问题,我该怎么解决这个问题?大家关于提高速度有什么经验或这方面的资料吗?

(图片不清可点击发大)

这是我作仿真时消息框内的一条警告。后来我换用了stratix系列器件作仿真,还是有这条消息。我怀疑是内部的连线较多而且信号的速度较快对布线有影响,就是说两个模块之间的连线很多,对于用什么样的可编程器件在这两个模块之间都不好布线,所以改过器件后还是出现同样的问题,我该怎么解决这个问题?大家关于提高速度有什么经验或这方面的资料吗?

器件内部时钟问题?

你要从report里面找出关键路径,针对代码具体分析,而不能简单地升级器件来解决这个问题。

器件内部时钟问题?

哦 我看看 谢谢了!

器件内部时钟问题?

需要根据REPORT来加约束,再重新布线,可能就OK了。

器件内部时钟问题?

我看了REPORT 发现时钟路径很长 再有就是当时程序写的有些乱,我就把程序模块化了,这是不是会影响时钟?

器件内部时钟问题?

呵呵...解决了,是我的一个模块仿真时时钟频率高了,还好这个模块实际不要这么高,降下来就没有提示了,谢谢bravelu 小编和serene 朋友,但是这种“需要根据REPORT来加约束,再重新布线”我还是不会用....