CC1121使用swrc253e rx_sniff_mode 例程的问题

1. 测试前准备

测试使用的寄存器配置与官方例程swrc253e 中的cc1120_rx_sniff_mode中的寄存器配置一致,我仅仅将MSP430换成了其他MCU,具体配置如下:

{CC112X_IOCFG3, 0xB0},

{CC112X_IOCFG2, 0x13},

{CC112X_IOCFG1, 0xB0},

{CC112X_IOCFG0, 0x06},

{CC112X_SYNC_CFG1, 0x0B},

{CC112X_DEVIATION_M, 0x48},

{CC112X_MODCFG_DEV_E, 0x05},

{CC112X_DCFILT_CFG, 0x1C},

{CC112X_IQIC, 0x00},

{CC112X_CHAN_BW, 0x04},

{CC112X_MDMCFG0, 0x05},

{CC112X_AGC_CS_THR, 0x32},

{CC112X_AGC_CFG1, 0xA0},

{CC112X_SETTLING_CFG, 0x03},

{CC112X_FS_CFG, 0x12},

{CC112X_WOR_CFG0, 0x20},

{CC112X_WOR_EVENT0_MSB, 0x02},

{CC112X_WOR_EVENT0_LSB, 0x14},

{CC112X_PKT_CFG0, 0x20},

{CC112X_RFEND_CFG0, 0x09},

{CC112X_PKT_LEN, 0x7D},

{CC112X_IF_MIX_CFG, 0x00},

{CC112X_FREQOFF_CFG, 0x22},

{CC112X_FREQ2, 0x6C},

{CC112X_FREQ1, 0x80},

{CC112X_FS_DIG1, 0x00},

{CC112X_FS_DIG0, 0x5F},

{CC112X_FS_CAL1, 0x40},

{CC112X_FS_CAL0, 0x0E},

{CC112X_FS_divTWO, 0x03},

{CC112X_FS_DSM0, 0x33},

{CC112X_FS_DVC0, 0x17},

{CC112X_FS_PFD, 0x50},

{CC112X_FS_PRE, 0x6E},

{CC112X_FS_REG_div_CML, 0x14},

{CC112X_FS_SPARE, 0xAC},

{CC112X_FS_VCO0, 0xB4},

{CC112X_XOSC5, 0x0E},

{CC112X_XOSC1, 0x03},

2. 现象描述

电流波形:和SWRA428A文档中描述基本一致,每隔大约16ms有一次脉冲。

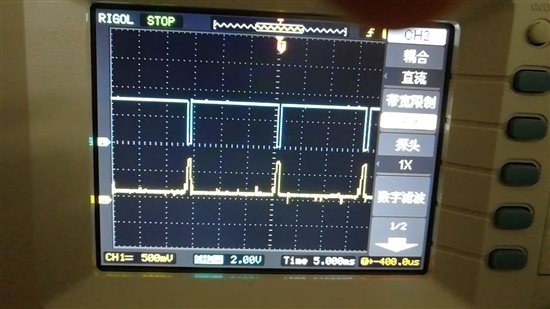

测试GPIO2的波形,在没有正确包的接收到的情况下一致保持低电平,但是GPIO0为什么一直输出脉冲(CC112X_IOCFG0 = 0x06,GPIO0波形图如下图),在手册中似乎没有描述。请问这是不是正常的?,如果不正常,该怎么改

其中,黄色为电流波形,蓝色为GPIO0的波形。

时间轴放大后如下:

3. 问题:

还有一个问题:请问使用了SWOR指令之后,在没有监听时是处于SLEEP模式还是IDLE模式?

你把GDO0设置为0x06,信号反转的触发条件为:

RX: Asserted when sync word has been received and de-asserted at the

end of the packet. Will de-assert when the optional address and/or

length check fails or the RX FIFO overflows/underflows.

TX: Asserted when sync word has been sent, and de-asserted at the end

of the packet. Will de-assert if the TX FIFO underflows/overflows

但是我并没有发送任何数据包。GPIO0在我没发送数据包的时候不应该有这样的脉冲。 另外,当我发送数据的时候波形和之前的并没有任何变化