环路的相位噪声问题

设计的是一个10G-20G的环路,50MHz鉴相频率,用HMC983+984方案,环路带宽在1MHz以上

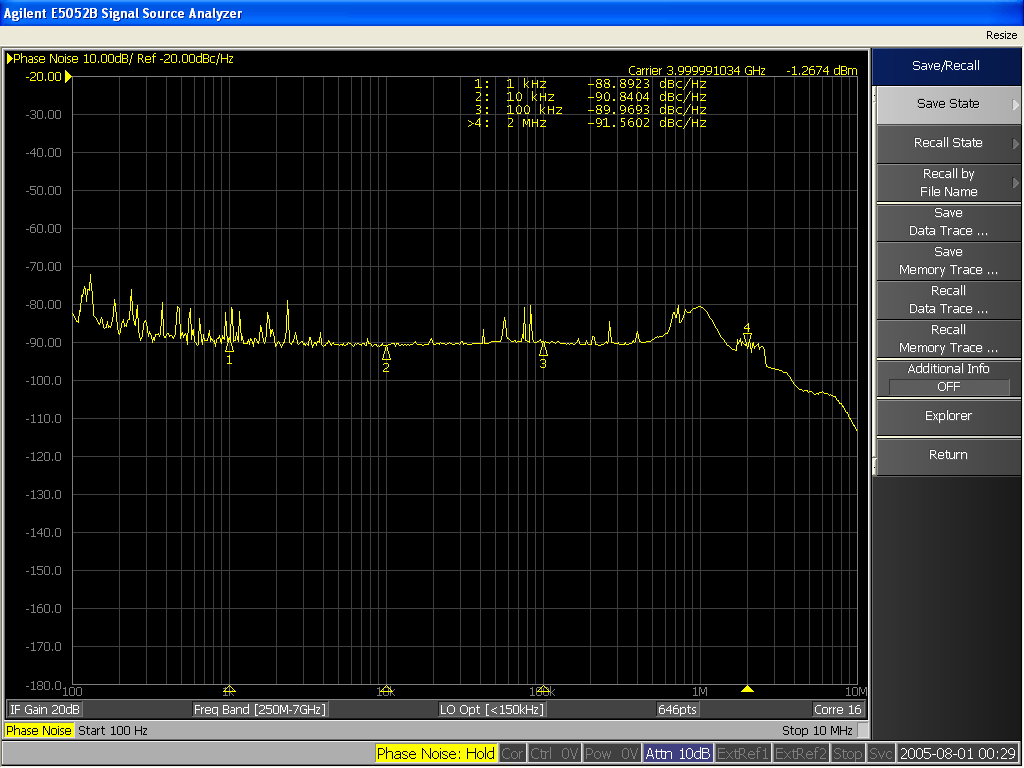

用安捷伦的5052B测相位噪声,发现在环路带宽内的相位噪声的抖动很大,在100Hz到100KHz的范围内可能从理论值的110dBc/Hz到90dBc/Hz,(以分频后的4GHz测试)。同时用频谱仪监测,发现相位噪声恶化的同时,频谱仪上的信号的噪底也会变差。

这个噪声的变化是随时都有可能的,从相噪图上可以看到慢慢的变差,然后又会变好。

曾将板子的电源全部用线性电流源供电,然后上电自动锁定后,FPGA不工作,单独接100MHz的频率源,发现都没有改善。

HMC983+984的控制字按照ADI的技术支持人员给出来的,理论上应该不会有问题,也做过修改控制字,但是发现也改善不了。

如果相位噪声不恶化的话,板子性能和指标都和理论值差不多了。既然能达到110dBc/Hz,肯定说明硬件上没啥大问题,要是干扰的话,全部电流源供电,数字电路不工作,在想不出有啥干扰。

也考虑过环路带宽过大,但是减小带宽,发现还是有这个问题。

当时选用的有源滤波的放大器是THS4031吧,100MHz带宽,怕是太大,减小成OP27也没改善。

我就纳闷了,上电后,发送完控制字,就是一个VCO,分频器,检相器,环路滤波器工作。前三样都是芯片,环路滤波器也不能让噪底变化来变化去吧。

请版上的牛人指点下,还能从那个方面去考虑。

可惜微波版挂了

把环路带宽再搞小点儿?是不是还是环路不太稳定,有点儿冲击就振一下?

另外,vco控制电压附近有没有什么干扰源?

找个大容量电池做低内阻电源供电,整个屏蔽起来,看还有没有噪声。

再有就是弄两块相同的板子,看噪声之间的相位关系和幅频关系,

判断噪声源在板子上还是在板子外。

按这个思路,类似的方法有很多,可以用来定位噪声源。

zan

其实调什么板子都应该做至少2块一模一样的。。。

出了问题可以马上换一块,看看是不是也有相同问题

1M处凸起那个9成是因为带宽太宽;

除此外未见明显异常

小数分频还是整数分频?

用的电解电容做电源去耦?

一步一步排除 先从最小系统开始做 在保证电源没有问题的前提下 先测试采用无源环路滤波器的整数分频 再上有源环路 再上小数分频 这两个器件比较新 仔细读读文档

带宽缩小过的,环路很稳定,怎么冲击,也都锁定在那个频点,只是放着观察,也会抖动。

如果是控制电压附近有干扰源,哪儿产生的呢?数字电路都不工作,要是模拟电路的干扰的话,又一点规律没有

恩,带宽要很宽, 理论是110的相位噪声,实际测会是90

着就是异常啊,但是也有到110的时候,

小数分频

恩,这个是个好思路,不过也就没试过无源滤波器,一直想明白为什么会时好时坏

还是没好 如果有时间可以过来找我 我帮你看看能不能帮忙解决

电池还是比你用的直流电源强

带宽为什么要很宽

什么叫做也有到-110的时候,你这图里带内不是稳定在-90吗

还有你的描述也很奇怪,什么叫做开始变坏后来变差,你是指纵轴的数值随横轴的变化

吗?synthesizer本来噪声就是随频率变化的

你凭什么认为是-110的噪声?做过相位噪声系统(synthesizer系统)仿真?

小数分频带内噪声长起来通常是因为鉴相器死区问题

但是你用的模块,所以理论上不应该存在死区问题

先单独测测晶振的相位噪声,它的恶化会直接导致synthesizer带内噪声恶化

恩,谢谢哈。今天用整数分频看了下,没有改善,我在青岛,不在北京啊。自己在鼓捣下,不过这个对项目影响不大。就是自己想弄明白。

要速度快,做矢网的激励的。所以带宽做宽。

图片是稳定在90,这是差的时候。好的时候在110。直接看的相位噪声曲线。没有仿真啊。

理论计算就应该在110多点。984噪底227,50M鉴相恶化77,4G倍频恶化38。理论就是112。

实测有在110的时候。但是不稳定会变化差到90。如果在105到110附近,我到觉得是正常波动。但是这个太大了。直接看带内曲线,或者选择10k频偏都一样