有遇到过串扰问题的不,请教信号完整性的问题

时间:12-13

整理:3721RD

点击:

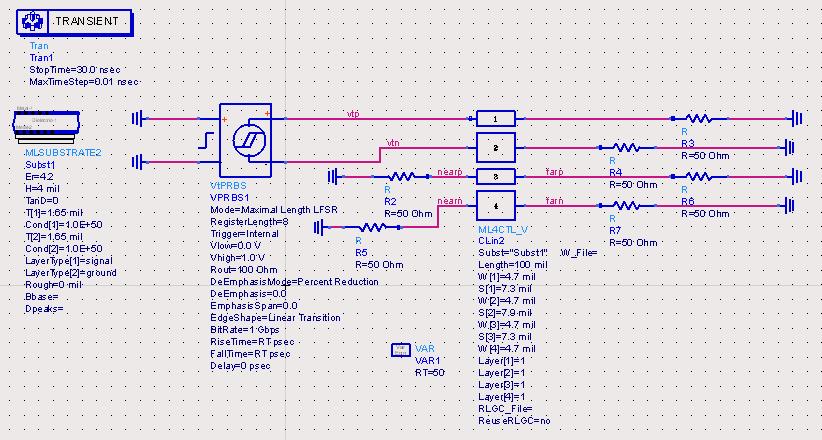

一直对走线间距没有概念,只知道按照3W来走一般没问题。但是最近画板子走线间距

比较近,不确定能不能正常工作。

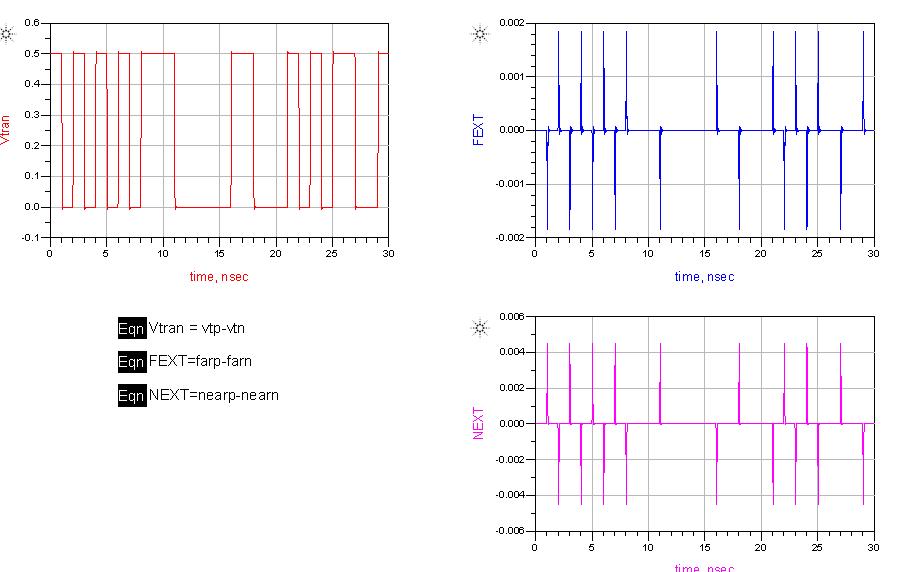

用ADS仿真了一把两对差分线的串扰,发现很小啊,几乎可以忽略(距离大约有2W),

不知道最终结果咋样。

你们碰到过串扰厉害导致没法工作的情况么。

比较近,不确定能不能正常工作。

用ADS仿真了一把两对差分线的串扰,发现很小啊,几乎可以忽略(距离大约有2W),

不知道最终结果咋样。

你们碰到过串扰厉害导致没法工作的情况么。

有,曾经在项目中将i2s走到了dcdc的switch node下,导致严重的crosstalk,以致于出来的声音有问题。

你这是不同层的串扰吧。一直觉得低速信号随便走线,现在看来也不完全是这样。串扰主要看的是信号的上升下降沿而不是周期。只是低速信号的串扰占空比小而不至于使接收端在建立保持时间内误采。不知道是不是这么理解。

从你这个例子看低速串扰了,有没有在接收端把时序往窗口中间调整调整试试?

理解错了,应该调整也没用吧,两个信号时延不具有确定性

不是低速串扰啊,就是你说的上升沿下降沿,与周期无关。dv/dt与di/dt啷。

我说的低速,是指数据速率低速。

重画板子解决的?你这不同层的信号是平行走的么

差分线干扰或被干扰的概率都小很多。

重画板子。没有平行,只是穿过