500MHz采样的FPGA问题

时间:12-12

整理:3721RD

点击:

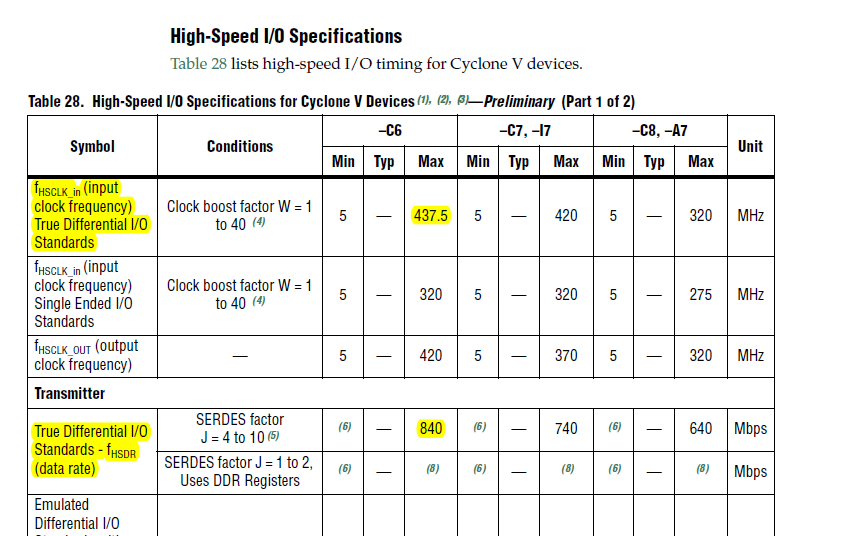

我用了输出数据和时钟都是500MHz的AD9484芯片,想用cyclone 5系列的FPGA接收该数据,但发现FPGA的f_HSCLK_in小于500M,而差分接口的数据率大于500Mbps,这种情况下该FPGA还能用吗?

换Stratix

stratix太贵啊,用这个cyclone 5应该也可以吧

这种差分接口为什么还需要解串因子呢,AD输入的直接就是8位并行数据啊

这种高速ADC是SDR的?我做过1.2G采样的,不过是DDR的,当然芯片也是virtex系列的

对,ADI公司的,不明白为什么是SDR模式,以ADI公司的实力做个DDR模式有什么难的

500M的信号,一般的示波器还测不出来呢