请教一个锁相环相噪的问题

时间:12-12

整理:3721RD

点击:

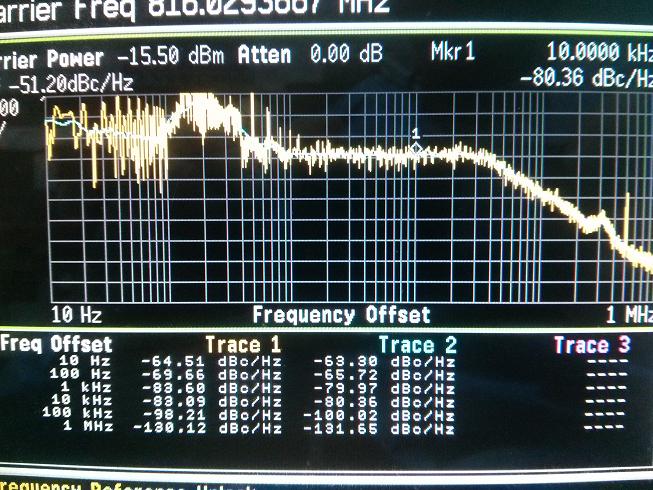

用ADF4360做频综,10MHz的温补晶振,给到鉴相器的频率为2MHz,VCO输出816MHz。

环路带宽为10KHz,CP输出为最大值。

在扫相噪的时候,从10Hz到1MHz,在100Hz的偏移出有一小段明显的鼓包,

请大家帮忙分析下这个现象可能是由什么造成的,多谢!

环路带宽为10KHz,CP输出为最大值。

在扫相噪的时候,从10Hz到1MHz,在100Hz的偏移出有一小段明显的鼓包,

请大家帮忙分析下这个现象可能是由什么造成的,多谢!

电源纹波

VCO改用直流稳压电源供电了,应该不是电源的问题。

现在怀疑是环路滤波器的问题,三阶无源滤波器,是不是和系统的零\极点有关,这块还没搞太清楚。

求助!

更改一下环路滤波器的带宽,具体你可以到ad官网下一个专用的环路滤波器带宽计算软件。

拍了张照片,近端很差,200Hz处有明显鼓包

看看晶振有问题么

.102

参考频率与晶振电源是共用的嘛?

用信号发生器提供参考时钟也是这样子,不过一直给的是正弦信号,没有用方波。

感觉是电网耦合进去的干扰。

我原先也有类似的经历,具体参数记不太清,就是在50Hz、100Hz附近有突起。

当时经常用测试仪器的人解释说是测试环境没有做电磁屏蔽所致。