请教采样调理电路隔离与抗干扰问题

时间:12-12

整理:3721RD

点击:

一般出于抗干扰和安全考虑,在采样时要求强电和弱电隔离,但是在一些简单电路中隔离

成本会相对比较高,见过一些设计中用运放做差分电路来实现。

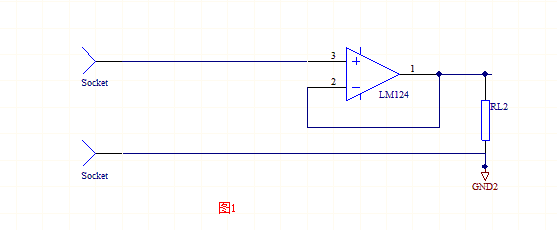

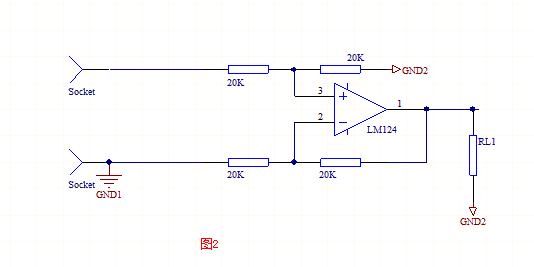

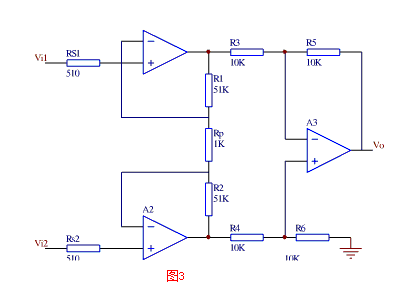

图1是跟随电路,明显的共地,图2和图3是两种差分电路。

请问,这两种差分电路对隔离和抗干扰能起到多大的作用?

成本会相对比较高,见过一些设计中用运放做差分电路来实现。

图1是跟随电路,明显的共地,图2和图3是两种差分电路。

请问,这两种差分电路对隔离和抗干扰能起到多大的作用?

差分线是为了抗共模干扰,要求器件共模抑制比较高才有效。

1、非对称差分线路,或者说根本不是差分放大,典型的单端。

2、典型的差分放大,也非对称,效果不如3。

3、典型的仪器放大器,输入高阻,对称。

有专门的线路驱动器,也就是差分缓冲电路,一般只有高速数字信号才用差分线。模拟一般都用单端的,至少要转换成单端线性的。

差模干扰,一般涉及电源方面,解决方法就是共模电感或者封闭大面积铺地;

共模干扰,一般涉及信号领域,解决方式就是使用差分信号,线对要等长且尽可能的小间隙(否则就变成差模干扰了)。