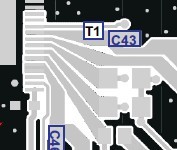

protel中怎么画这种宽度渐变的线?

粗线——过孔——细线 ——添加滴泪——删除过孔

.28

直接按铺铜画呗

这样看上去不会很平滑吧?

目前这是能想到的最好的办法,虽然弄起来也不那么好看~~

同认为敷铜是最好的方法,

如果用Altium Designer,可以按Shift+空格变换线型,

可以绘出直线型或弧形的轮廓,很方便。

谢谢,目前就是这么用的~~

现在感觉用solid region更方便,可以精细调整。

不过话说这种渐变线除了装?一下以外,有什么实际优点?

不是装。

有些电流大的走线需要线宽比较宽,但是引脚刚出来时空间有限,不能把线宽搞得比较大,只能逐步加大,否则线路电阻就可能比较大,电流承载能力也会很弱。

最近在做一个电机驱动的板子,TI公司的原装电路板上就是这么绘制的,觉得这个很有用。

对

这个挺有用的

有些器件或者模块的管脚很密,没办法直接走很宽的线

所以逐渐变宽很重要,我是直接分段调整线宽,很难看

你用solid region做这个,可以调整得非常平滑,做到比较美观。我摸索了一阵子,总算找到这个工具来解决这个问题~~~

ok,多谢

回去我试试

为了减小信号反射,高速信号在不同线宽的传输线过度过程中会用到。

做工程的表示好像这个用不到

就连intel的demo板,用DDR3也是直接变线宽

渐变线宽的差分对,为了控制阻抗,怎么控制线间距呀...

那是因为DDR3不需要用这种技术。

Serdes大于10Gbps的,margin是每ps每mV抠出来的,必须这么做。

这种渐变线通常很短,不需要严格控制线间距。但是和板厂的沟通非常重要。

broadcom/marvell/intel/altera对10G serdes的design guide我没发现有这么做的

我们实际做的10Gserdes也没说有渐变线宽的....

如果你能找到相关规范还请提供个链接,谢谢了

你margin较大的话,没有人要求你一定这么做。

如果你的背板设计很受限,比如connector为了兼容老的connector很挫,因为成本的原因,背板材料很挫,或者走线和过孔因为空间的原因受限,你1ps,1ps的扣margin,只能面面俱到。如果你用了顶级的connector,magtron6的材料,40层以上的背板,就当我没说过吧。

具体规范需要仿真得出一个平衡的渐变线设计。

by the way,design guide不是万能的。它没有cover的地方很多。很多东西都是要自己根据应用的情况,自行仿真决定的。

把你说的总结一下,简单点说,做工程的没人做渐变线....

所有设计必须遵照厂家的design guide,否则出了问题人家只会建议你改一板再试试看

by the way,你知道何种软件可以准确做渐变线10G信号的仿真?ansoft?

我回答你的问题。

1) 工程中有用渐变线,难点是和板厂的沟通。

2) guideline中提到的,你可以去遵守,没有提到的,你需要自己想如何优化,没有哪个guideline可以面面俱到,比如这个渐变线,一般guideline不一定会提到,我可以说一个你更觉得夸张的,渐变的过孔焊盘在某些情况下也可以使用,or你可以故意作一些阻抗不连续的地方来抵消一些不可抗拒的反射。这些大多都不是follow guideline的,有些时候guideline列出的case是不可能实现的,难道我们还因为这个不做产品了?

此外很多厂商的guideline都没有定量指标,什么叫尽可能的短?什么教阻抗尽可能的连续?什么叫尽可能的粗?这些本质上都是废话,具体的limit还是需要case by case的study。

而且,你也可以challenge guideline,上面写的也不都是对的。因为很多rule都是有前提应用条件的,说多了,以讹传讹,就把前提应用条件给丢了,这种情况很常见,包括你列出的大厂的guideline。如果把guideline当bible,那么系统厂商的SI工程师存在的意义在哪里?当然实际工作中,时间紧任务急的时候不会去搞这么细,但是没有cover到的地方,设计起来也是有门道的,需要自己摸索。

3) 渐变线可以用HFSS和CST作仿真。我用CST多,而渐变线也不是Serdes的设计难点,更复杂的地方是via相关的区域。

谢谢您的回复,我不做Serdes,但是对这种问题比较感兴趣,一定程度上也用得到,

之前我测试高速的DAC时对PCB设计关注过,发现SI对测试结果影响很大。

多谢wstl,学习了。

我印象中,线间距越小、线越宽,阻抗就越小;

这么说来,我的一个理解是,

似乎渐变线和线间距的配合的确值得进一步琢磨,甚至有种可能,在某些情况下,

渐变线和线间距的配合设计可使特征阻抗在不同线宽的过渡过程中保持基本不变...

但是在目前PCB厂家的情况下,这个太难以控制了,很容易出废板...

我之前做的板子还不到2GHz,线都是自己bonding的,没有高速信号的VIA,

也就没考虑这么复杂。

再次感谢版上的牛人们,哈哈。