请问高速ADC的时钟对电源干扰问题

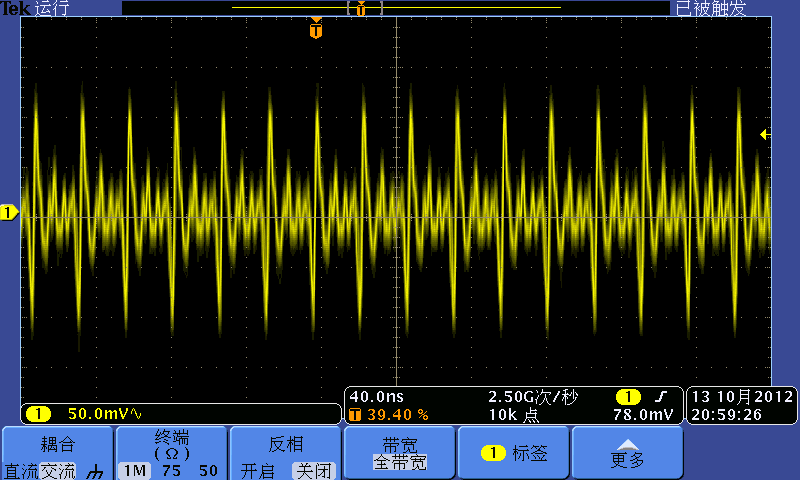

但是这样可以工作室发现,+5VA因为FPGA给ADC的20Mhz变成较大的噪声了,如图2所示,有+/-100mV,频率为20MHz;如果我让FPGA禁止给ADC时钟,那么+5VA噪声与输入相当<20mV。 我模拟部分的电路对噪声很敏感,请问这样该如何解决,或者是否我的电路布线有不合理的地方?

谢谢

先把adi的开发板图看明白了再来问,有条件就买一块原装板子

ADC的时钟很重要,要当做模拟信号处理;从FPGA输出的时钟会比较脏,不建议这么接

1、可能是地层分割的影响。如果采用完整的一张地层,通过布局布线保证数字信号及回流不流经模拟区域,则噪声应该会小不少。

采用一点接地时,最好通过一定宽度的PCB实现,而不是电阻,并且所有数字信号应位于该接地点上方。

2、+5VA应该由+5V经LC滤波得到,磁珠的电感值是否合理?

3、上述噪声也可能是测量过程中,示波器探头受到的干扰。对噪声的分析最好还是通过采样数据进行。

另外,楼上的说的对,时钟信号最好采用通过buf芯片给出,其余数字信号也可buf一下,保证与AD芯片连接的所有信号是干净的。

关于最后一句,我的做法是FPGA出来给AD/DA的数字信号都过个磁珠,如果发现有问题就调整磁珠的型号,干掉主要的噪声。

你的clock和D[10:0]是不是跨分割了?

地分割这件事情,不要随便用,网上的各种所谓的经验很多都是错的。

补救措施,如果真的跨分割了,你在信号线跨分割的地方,多用几个电容连接信号跨过的两边的plane。

容值的选择:电容的谐振频率和主要噪声分量频率重合,但是要注意电容的安装电感的影响,自己可以多试几个电容

在其次就是串扰的问题。

最终再看电源网络的设计问题,你的去耦作的如何。

又见到一个地分割的受害者

谢谢指点,pcb实际布线和我前面的框图大致相同,adc的CLK和Data确实是跨分割了,所有的回流信号都经过图中所示的0欧姆电阻,看来这部分有很大问题。现在尝试你说的补救措施。。

记住这种跨接电容要多加几个,均匀分布在所有跨分割的信号中。

所有跨分割信号中?这在目前的电路板上很难做到,两个区域跨分割的信号连接点附近基本没有GND/GNDA裸露出来.

我今天按照你说的尝试一下。同时按照前面网友的意见考虑改进电路板:计划GND平面不再分割,一块电路板有一个完整的地平面,FPGA与ADC的CLK和DATA都串联一个磁珠;但是数字电源/模拟电源还是采用区域分割的办法。

请问这样有没有什么问题?

如果跨分割很多信号线,且ADC精度要求很高,还是重做板子吧。

完全地平面,分割电源,但是没有任何信号跨电源的分割。

电源平面和地平面是相邻的。

电源平面靠近IC。

就可以了。

具体叠层还要仔细分析。

现在正在弄得是四层板,顶层和最底层走信号,第二层是完整的地平面,第三层是分割的电源层,分别分割三个区域,如第一个贴的图所示,分别是+5VA区域(模拟部分),+5V区域(数字部分),+3.3V区域(FPGA部分 )

FPGA与ADC连接可能会跨越两个电源域: +3.3V和+5VA,所以我将这两部分的分割在ADC器件的下部了,确保FPGA引出的CLK/DATA连接到ADC一直是在3.3V区域内,这样是否就可以了?

请问电源平面靠近IC是为什么?第二、三层分别放电源层、地层,会比分别放地层、电源层好吗?(我看到的另一个说法:因为顶层IC多,走线多,所以建议靠近顶层的第二层作为GND平面)