如何仿真开漏(Open Drain)IO口

时间:10-02

整理:3721RD

点击:

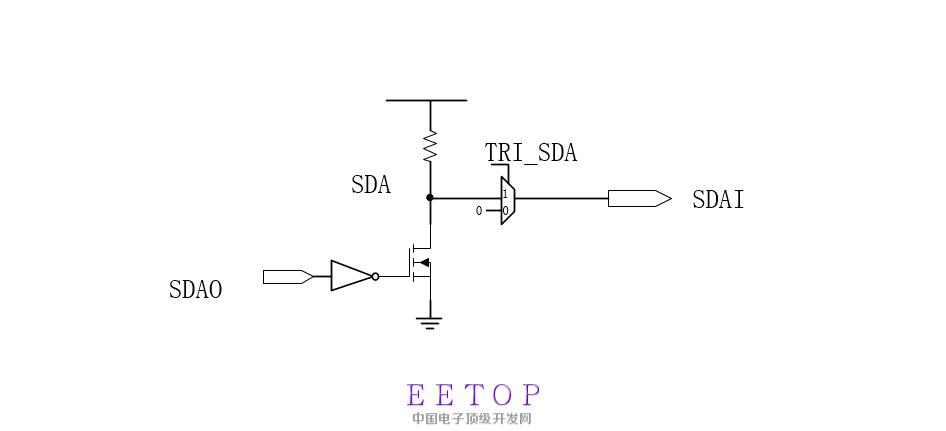

如图所示的I2C协议中SDA实际电路:

像这种带OPEN-Drain MOS及上拉电阻在纯verilog中仿真比较难搞,特别是同一总线连接多个器件的情况,但是可以近似处理

- //----for synthesizable block---//

- inout SDA;

- wire sdai,sdao,tri_sda;

- assign sdai=tri_sda?SDA:1'b0;

- assign SDA=sdao?1'bz:1'b0;

- //---------for testbench---------//

- inout SDA;

- wire RX;

- reg EN,TX;

- assign SDA=EN?TX:1'bz;

- assign RX=SDA;

- pullup pu(SDA);

不过这种近似还是不够准确,根据HDL标准,可以使用wire AND 线网

- //---综合电路中--

- inout SDA;

- wand SDA;

- assign SDAI=tri_sda?SDA:0;

- assign SDA=SDAO;

- //--testbench----

- inout SDA;

- wire RX;

- reg EN,TX;

- assign SDA=EN?TX:1'bz;

- assign RX=SDA;

此方式定义在仿真中只要有一边定义了wand线名,双向口就可以完全模拟如图所示的功能

请问什么是open-drain mos