DAC后仿的SFDR提高不上去

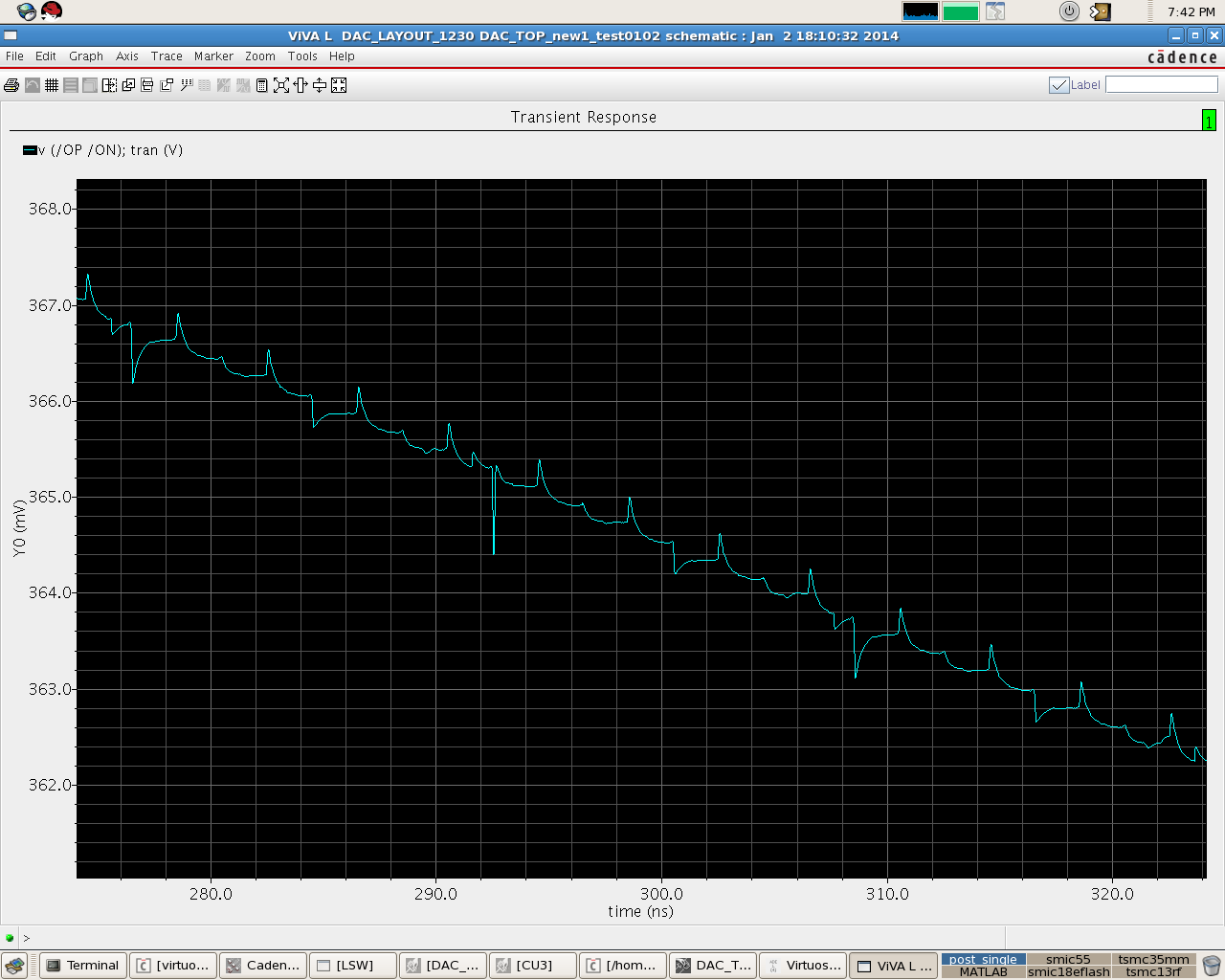

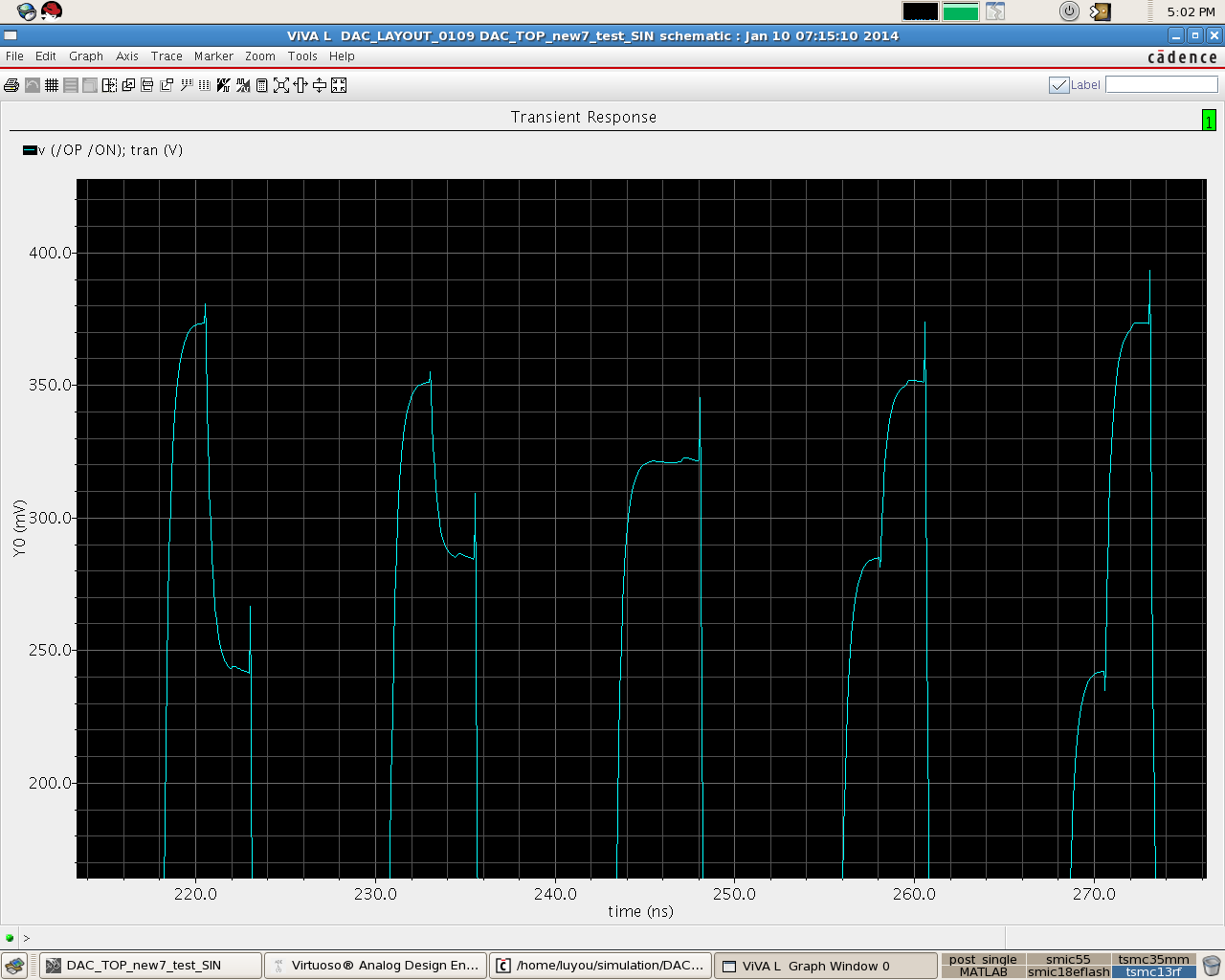

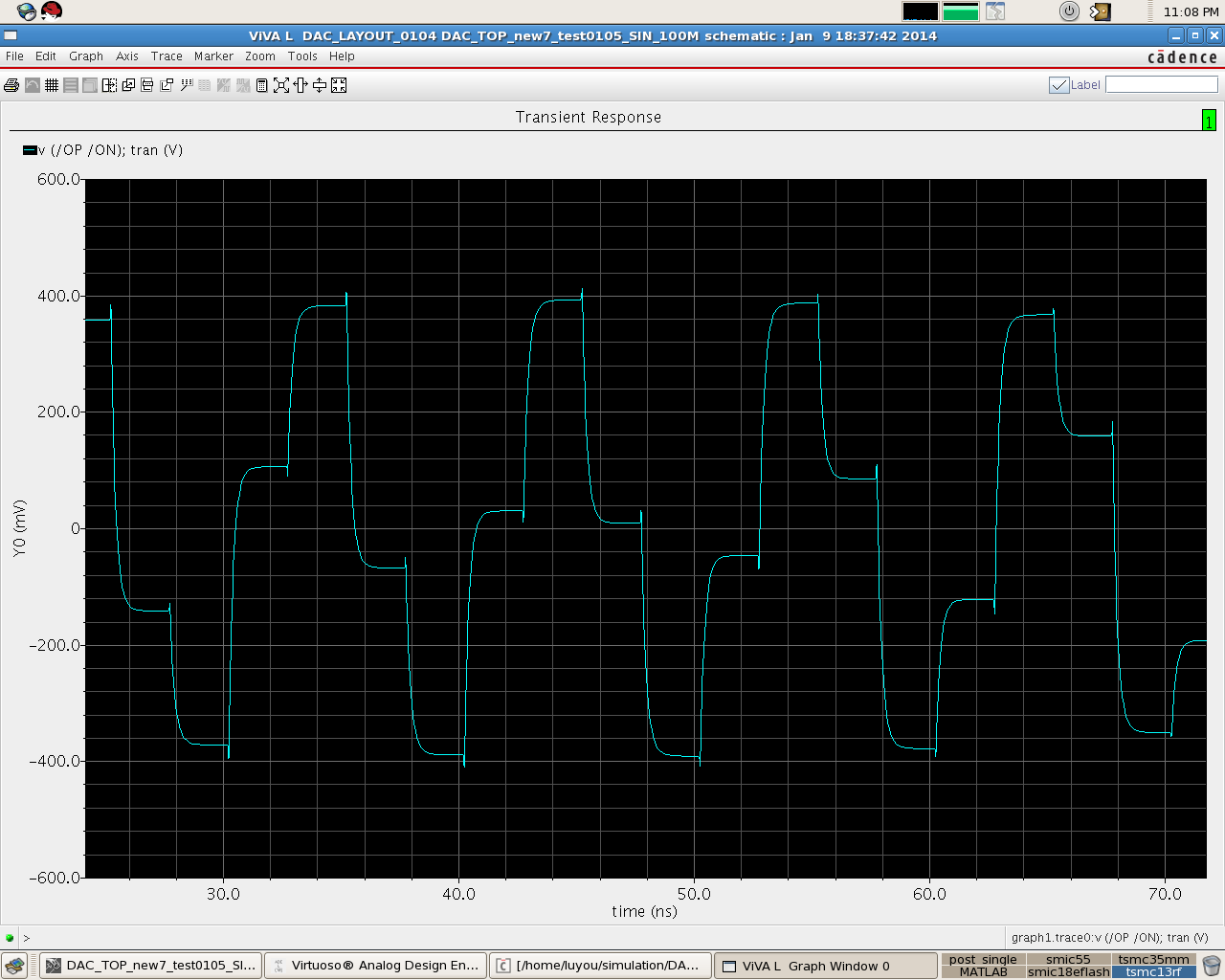

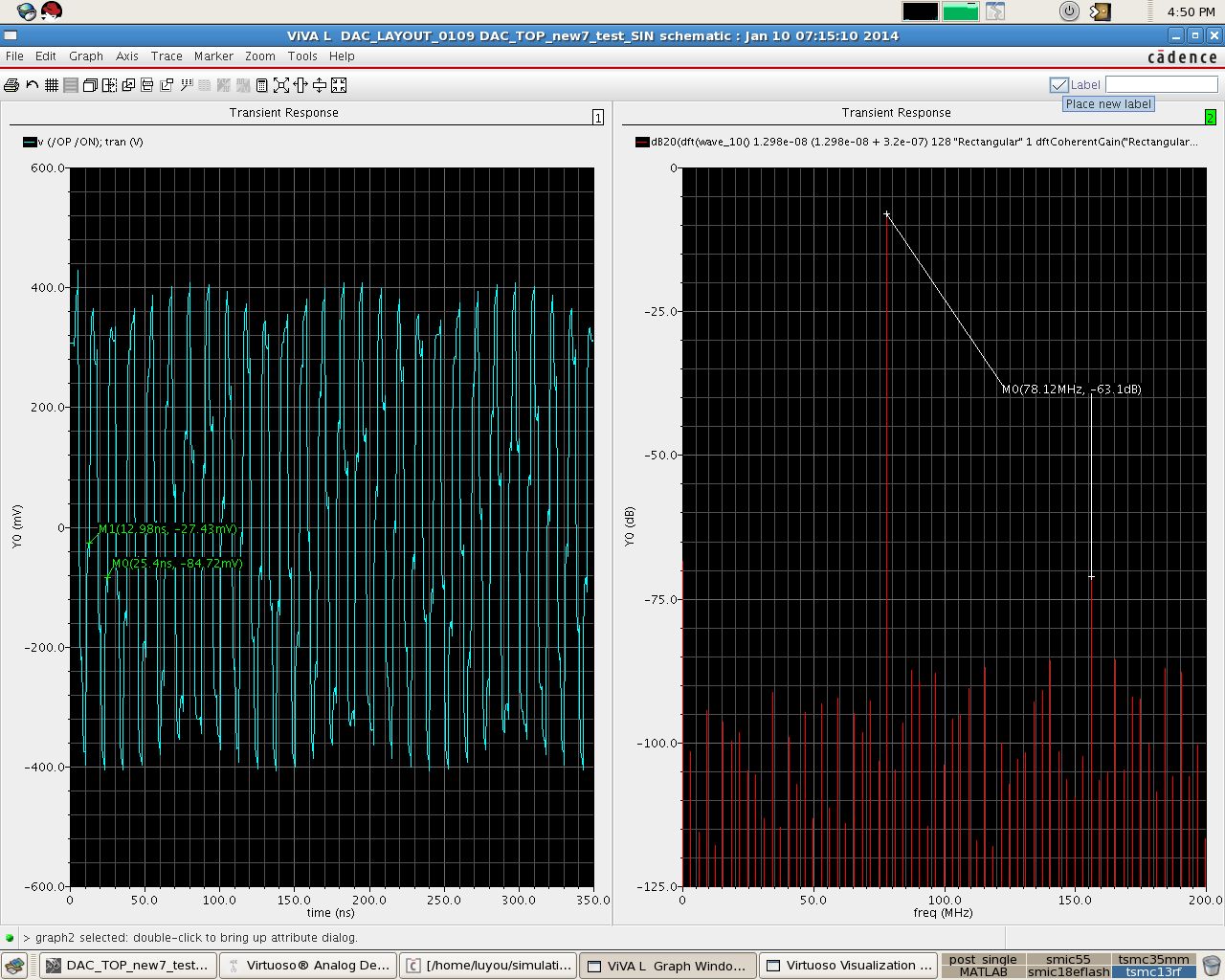

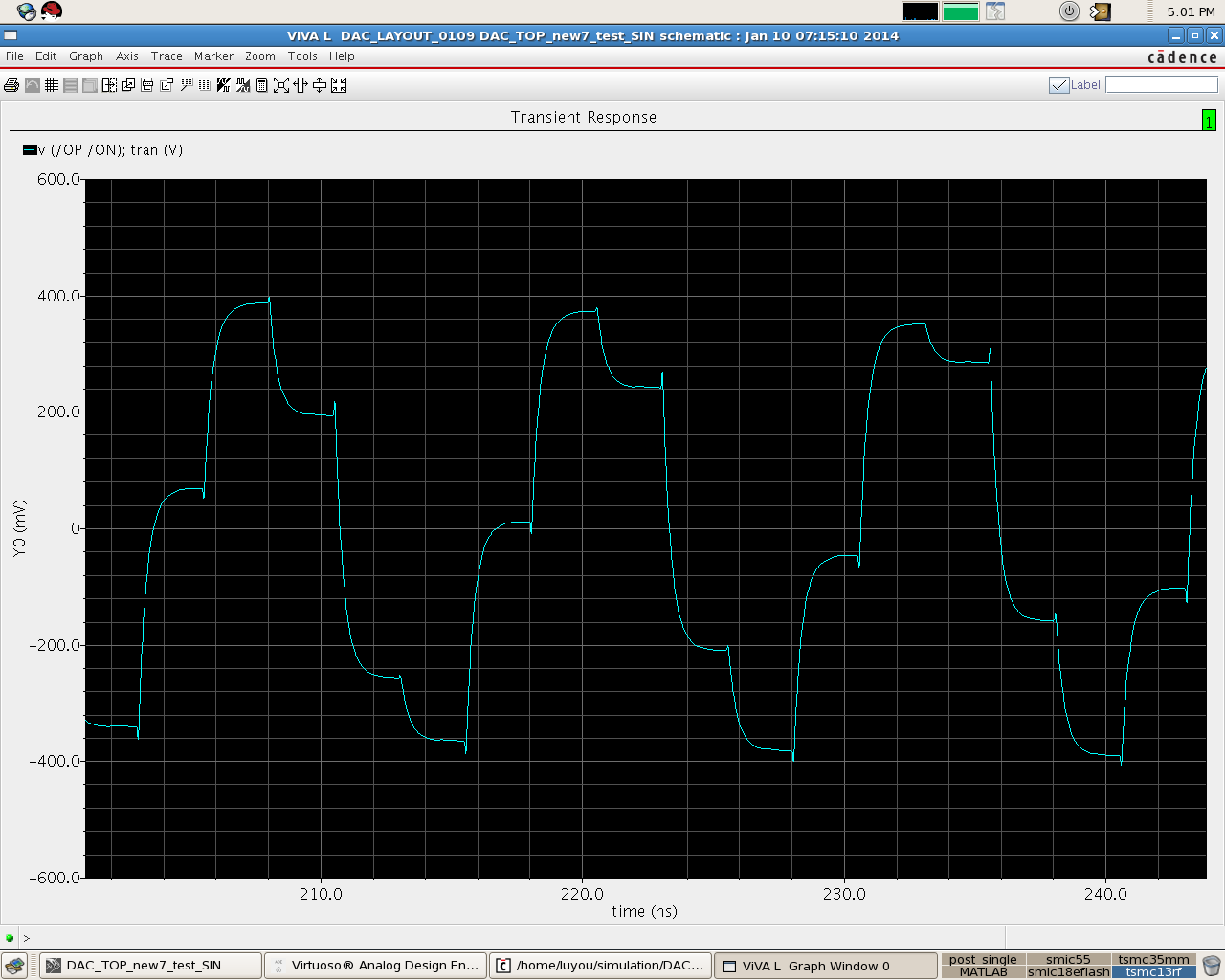

图片的顺序有点错乱。第一张是:后仿的斜波,第二张:仿sin放大的,第三张:前仿sin的,第四张:是后仿sin的SFDR结果,第五张:是放大的后仿sin波形。

光这几张图什么也看不出,只能知道指标没达到

建立不够,看看时钟有没有问题,延时匹配行不行,关键节点寄生是什么样的。,看这样子电流源阵列好像没什么问题吧?输出阻抗怎么处理的,输出是怎么处理的,直接接到电阻上?

多仿真,时间允许的话,100MHz信号,50MHz,30M,200M多跑几个。

时钟没问题吧,输出阻抗足够了应该,关键节点的寄生应该怎么考虑,仿斜波的时候每个台阶上的波动是寄生引起的吧?电路的仿真时没有问题的,现在的问题是版图上哪里出了问题导致的SFDR上不去,一开始会议室电流源下的开关切换的问题,可是看了一些开关切换的控制信号,匹配的挺好,没什么问题,所以现在比较犯难。

理论上问题应该是切换过程中出现吧,你看时钟匹配的挺好?你看的是某一路的差分时钟切换匹配?还是很多路同时切换?不同的输出组态,在时钟树上看到的负载是不同的,所以时钟到达每对开关肯定是不匹配的才正常啊(对于400MHzmps来说),周期性的切换不一致,就产生了谐波。我说的节点也就是开关位置,与电流源阵列连接的地方,这些地方寄生会引起每时刻电流源输出端的电压不同,比较敏感,不知道你们layout开关位置有没有考虑,至于开关交叉点放到低电平处类似问题,你应该不会犯这错误吧

没有看很多的开关时钟,看的是某一行的8个电流源的开关差分时钟,其中七个开关匹配的很好,有一个开关延时30ps(这个问题大么?),是说要把所有开关的时钟都看一下么?layout开关位置要怎么考虑呢,是避开其他的时钟信号么。电流源和开关管用的是p管,这样开关交叉点要放到低电平处,切换过程中,两个开关管开的快一些、关的慢一些,是么?看来你还挺了解DA的,请多指点指点,谢谢啦~

学习了 不知道能否指点一下layout的开关位置怎么考虑呢?