论如何允许两个元件重叠,而不出现警告(绿色)的方法

时间:10-02

整理:3721RD

点击:

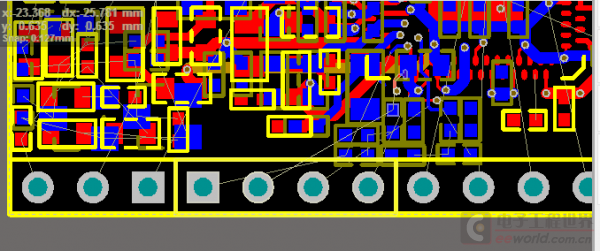

在绘制PCB时,需要将几个接插件并排紧密排列,如下所示,出现警告提示

之前也遇到过这个问题,当时采取的方式是重新做了个封装,将需要并排的多个元件做到一个封装上,显然,这种方式不仅要重新绘制元件原理图封装及PCB封装,还需要修改已经绘制好的原理图,比较繁琐,并不是一个最佳方案,上网查阅了相关资料,有下列方法可取:

1、取消DRC errors

缺点:取消DRC errors的方式会导致,出现连线错误时也不报错

2、修改rules:DESIGNE->RULES->placement 把 componentClearance Constraint 下的规则前面的勾去掉

缺点:把整个CLEARENCE规则全部取消,布件时发生重叠也会被忽视

3、在封装库里,把它们画成一个元件

缺点:繁琐

4、修改rules:添加新规则,对指定元件执行相应规则

推荐

参考网友建议,本次采用的方法是:不将整个CLEARENCE规则全部取消,而是在Clearance添加忽视对象规则,如下图所示(四个接插件分别对应P1、P2、P3、P4),当前觉得这种方式还是比较容易实现的,也比较合理,还有更合理的方式还望各位大侠指出

设置规则:

结果:

还有个简单的办法,我看你这个类似插针的么。直接做成一个封装,不就对了吗。还有这么麻烦。。。。。

我都是直接把间距设置为0,因为元件经常有重叠

楼上说的我常用

取消DRC errors虽然是个办法,但容易误解

常用2、修改rules

是的,是插针,之前是直接做成一个封装的,不过感觉这样不仅需要在对应的原理图库及PCB库中添加对应的封装,还要对原理图进行修改,不是很方便,所以就用这种方法了

这样的话,如果存在不应该重叠的元件重叠了也检查不出来了啊,一开始修改rules我是重新添加了一个规则,对指定的P1P4采用间距为0的设置,不过后来发现可以在默认规则中设置忽略对象,所以就修改为上述方式了,

其实我倒是觉得你的这种更麻烦,我说的那种,个人觉得简单粗暴。。。。

确实是简单粗暴

所谓的错误提示只是提醒用户这里有可能错误,如果你确定没错就让他发绿呗,有啥关系

问题在于看着难受啊,大概是有点小强迫症吧

给封装加3D

DRC关掉,检查出错时忽略就行了。个人感觉方便。