阻抗设置疑问?

时间:10-02

整理:3721RD

点击:

阻抗设置疑问? 看芯片手册,差分信号线需要设置阻抗,但是查看我们的产品布线,好像没有设置啊,前辈们阻抗控制都是怎么做的呢?

长线时需要设置,如果线非常短就无所谓。长与短的判断基于信号波长。

不太明白哦 DDR布线以及射频信号线都有差分走线

DDR3 800M吧 射频信号是2.3G左右的 要设置吗?

那是高频哦,频率越高波长越短,对高频而言的“长线”也就越短。

那当然要了,除非连线比波长短。这个在DDR3上不可能,因为内存条的尺寸摆在那里,线数又多,连线比较长是必然的。但在2.4G射频系统中可就不一定了,完全可以存在比波长更短的连线,那些短连线就无所谓了,执行就近原则即可。

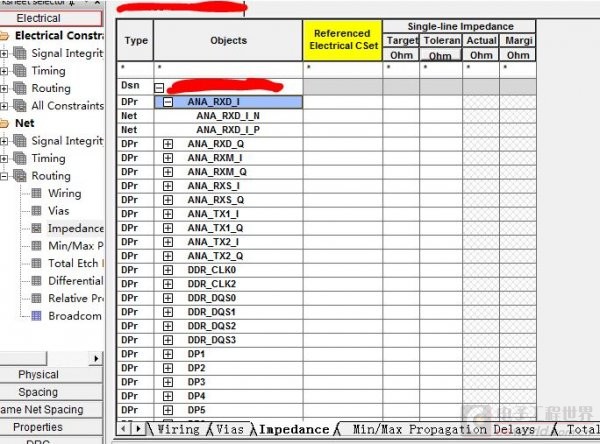

那我在ALLEGRO里面怎么没看到阻抗控制啊

高速电路要看时钟系统, 以波长看长度只适合共同时钟系统, 而对于源时钟系统就没有这个限制了. 我们的4通道万兆PHY, 4个2.5G通道并行传输, 最大布线长度可达3米, 通道间的长度差可放宽到5公分, 不要求严格等长.

这个需要人为处理。

是这样的。你们玩什么东东,居然要那么大带宽!游戏服务器?

用于服务器, 据说老板正在跟马云争取投5个亿...刀...

目前一颗芯片有5组4通道, 2组PCIe, 支持双主板服务器

支持PXE, 也可用于网吧, 网咖服务器

不过, 这事跟深圳这边没半毛钱关系, 所以我仍然不后悔3年前拒绝以年终奖换取深圳公司5%的股份

万兆以太网头一次听呢 不等长以及阻抗控制,数据传输能保证没错吗

腻害了

万兆以太网 是不是phy芯片很贵啊

前辈 那你是要了年终奖还是股份啊

有说过不需要等长, 不需要控阻吗? 8楼讲的那么清楚了, 你何不去查一下相关资料呢? 关键词: 源同步时钟

13楼够清楚了, 没必要重复