芯片底部走线,干扰情况,弱弱的疑问

时间:10-02

整理:3721RD

点击:

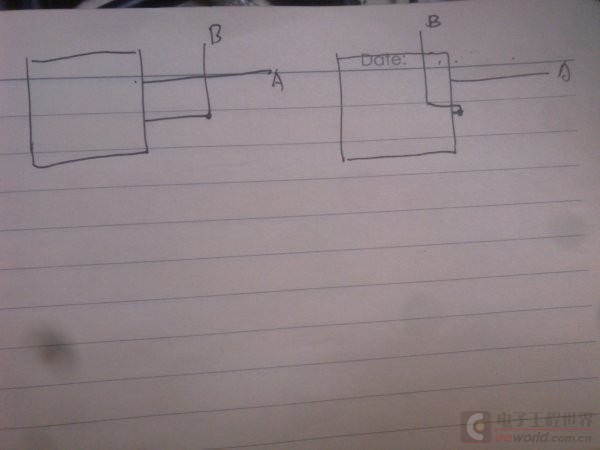

一个芯片,其中,两个引脚,是两个容易受干扰的信号A,B。和外部相连。假设芯片在正面。第一种情况,都向右延伸,两个信号会有交叉,按板厚1.6mm算。交叉点处,应该会有一些干扰。

第二张情况,信号A向右延伸,不变。信号B稍微向右延伸后,过孔到反面,向左,经过芯片底部,向上,延伸。这样,信号A受干扰程度应该减小了,但是,信号B呢?在背面,和芯片底部距离略大于板厚,这个情况,会不会受到来自芯片底部较大的干扰,还是,受到的干扰很小。

哪种方式更合适呢,请大师指教一下哈。谢谢。

第二张情况,信号A向右延伸,不变。信号B稍微向右延伸后,过孔到反面,向左,经过芯片底部,向上,延伸。这样,信号A受干扰程度应该减小了,但是,信号B呢?在背面,和芯片底部距离略大于板厚,这个情况,会不会受到来自芯片底部较大的干扰,还是,受到的干扰很小。

哪种方式更合适呢,请大师指教一下哈。谢谢。

对于小信号,更多考虑的是其它信号对它的干扰,只有强信号才需要考虑对其它信号的影响。

在芯片的内部,连接线的距离比PCB上要小得多。

对啊,我考虑的就是其他信号对这个信号的干扰啊。我就是不知道,两种走线,哪种,两个易受干扰信号,受的干扰更小。

我觉得左图会好一些

右图在芯片底下走线除非你能确定芯片内部的结构

否则不确定性太大了

另外是不是可以考虑使用4层板中间另屏蔽

或者如果选择右边的方案,要芯片低部的TOP层加一块地皮呢?

没那么多讲究,你喜欢就好

纠结局部没有意义,敏感小信号通路的布线原则是尽量的短,并尽量远离EMI源即可,彼此的交叉没啥影响。如果是高频信号通路,则应避免过孔,利用回路元件进行跨接。

恩,对于右图,芯片底部加一块地,应该好一些,不过,这是两层板,没特殊情况,不用四层。

谢谢,顺便再问一下,高频信号,近距离平行走线,容易出现串扰。是不是,近距离平行信号中,有一个是高频,其他频率相对较低,也容易出现串扰。两个电路板通过排线连接。其中有一个几十M频率的信号,与左右的信号距离0.5mm。排线长至少10cm。这样是不是容易产生串扰?

10cm线长确实比较长了,容易发生耦合串扰,不过也要看信号强度以及能接受的噪声,不可一概而论。在数字电路中几MHz到几十MHz的信号很常见,但用排线长线连接也很常见,故必须具体问题具体对待。

交叉点 相关文章: