电源去耦电容的选择

时间:10-02

整理:3721RD

点击:

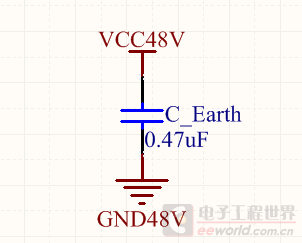

在网上看了一些资料了解到,电源对地一般要有个去耦电容,请问我在原理图上这样加去耦电容有问题吗?图二是我PCB去耦电容的接法,不知道这样用行不行?请教各位老师我选用的是0.47uf的陶瓷电容,不知道行不行?

应该可以,需要考虑电容的耐压值

原理图那样是没有问题,主要是PCB布线时尽量让去耦电容要与器件非常近,可以滤除输出信号的干扰。

如果选用同样容量的CBB电容行不行?耐压值可以达到400V

老师您好,但是我的板子上器件很多啊,应该与哪个器件挨着呢?

你要给哪个器件滤波就跟哪个器件电源脚挨得近些。。。还有GND pin要就近打VIA接GND

同样材质同样容量的电容器,耐压越高的体积越大,价格越高。

没有必要使用耐压400V的电容器,耐压100V已经足够了。

最好是每个大型芯片各设置一个电容,并且与该芯片就近联接。

有些大型芯片,手册中就注明有多个电源引脚,多个地线引脚。这样的大型芯片,每个电源引脚都应该用一支电容接地。

通常相差二到三个数量级,如0.1uF与10uF,在去耦电容的设计上,在PCB板空间允许的情况下,最好做到一个电源引脚分配一个去耦电容

但在空间不足的时,可适当削减电容的数目,具体情况应该根据芯片上电源引脚 的具体分布决定,因为厂家在设计IC的时候,经常是几个电源引脚在一起,这样可以共用去耦电容,减少去耦电容的数目

谢谢老师

谢谢老师

好的,谢谢

谢谢老师