今天我画的PCB被人鄙视了,谁能看一看

2. 谁能看一看我画的板子,有什么地方不好,我想知道那位同学说的是否属实,谢谢了。(铺铜隐藏了)

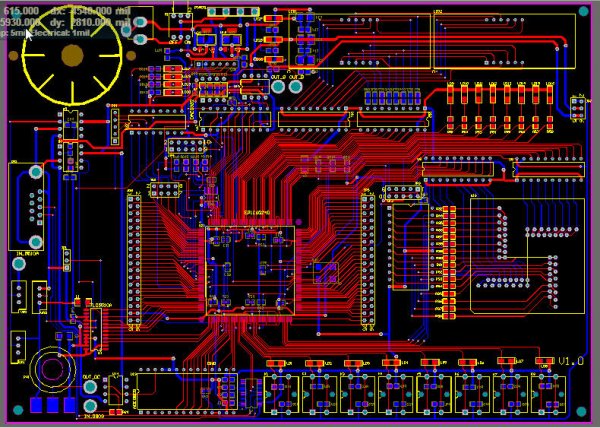

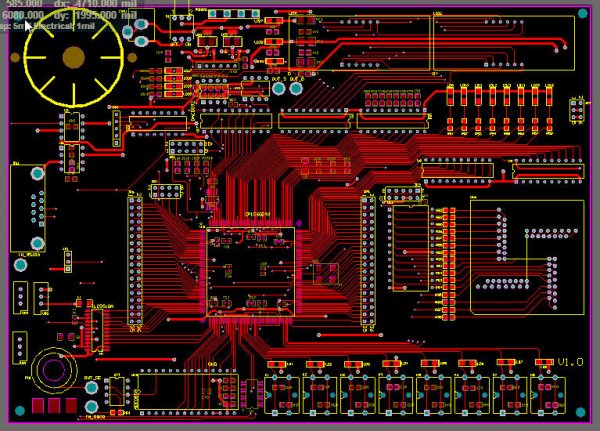

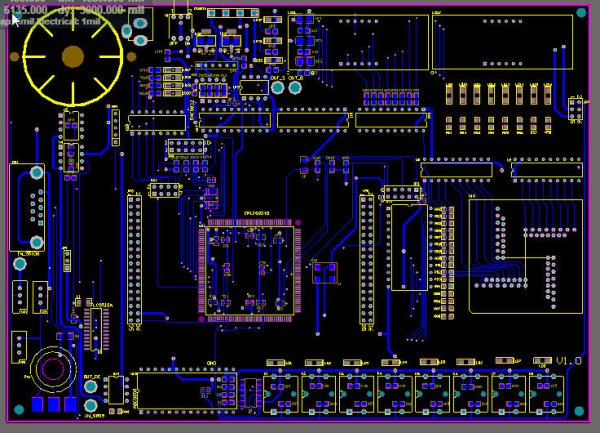

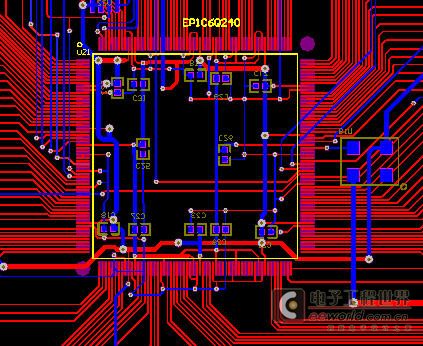

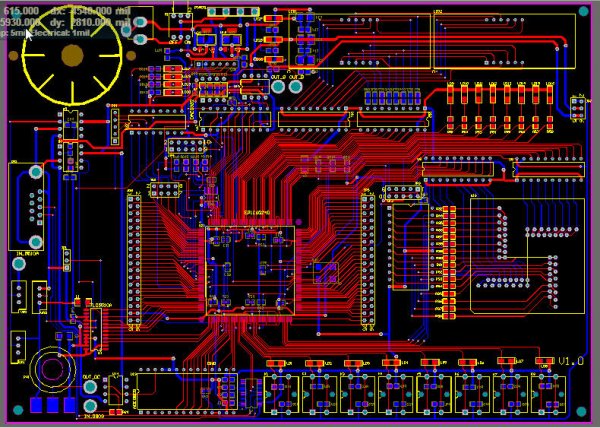

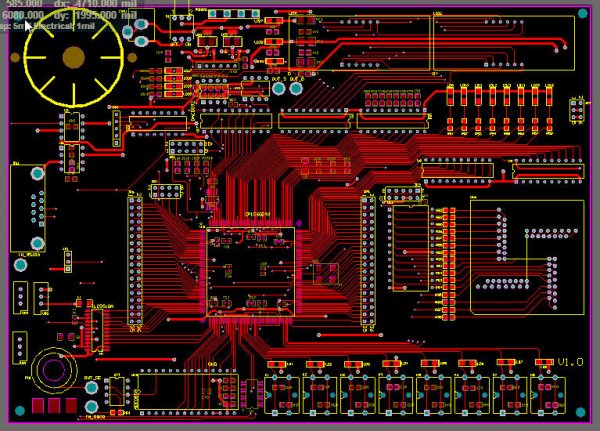

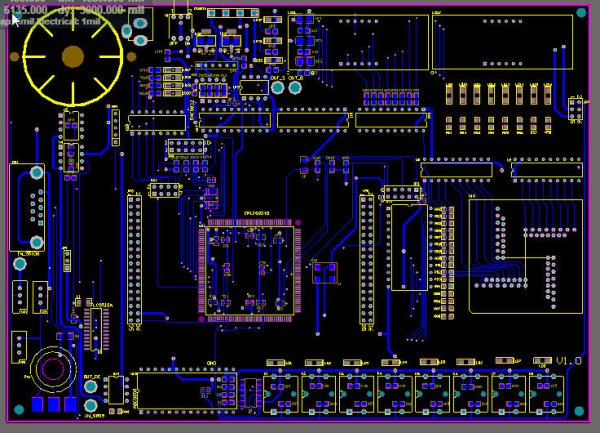

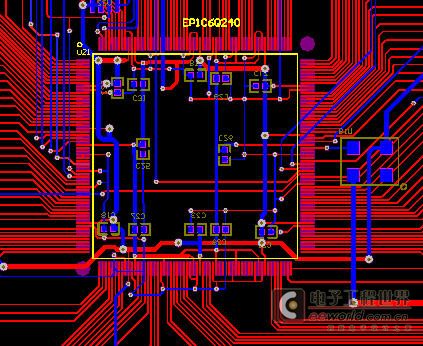

下面分别是 布线图+顶层布线图+底层布线图+FPGA部分 (双层板)

楼主画的还可以把,不知道那些细节是否合格呢,还是要鼓励楼主拿出来秀秀呀。

不知道板子大小是否规定了 器件有点稀疏

那个同学说的一点就是: 过孔多的一塌糊涂,其实只要一半就可以完成这个板子。 这话有有理吗?

FPGA的焊盘有点短,如果那是软件自带的库里的,那建议自己做个封装,否则焊时很麻烦;还有FPGA下面的电源走线太乱;某些器件的去耦电容和电感没弄,晶振的输出脚最好串一个小电阻;配置口太难找了,而且离其他元件太近,到时候会不能用牛角座。我也画了第一块FPGA板,出了不少问题,不过不出问题怎么能记住呢?

一、受力器件的焊盘最好包铜,比如DB9,电源,排针的焊盘最好包铜或加泪点。

二、如上同学所说,布局有点稀疏,可以再紧凑一些。

三、还有板子跨度太大,只有4个角有安装孔,担心插拔的时候压弯pcb,导致器件脱焊引起接触不良。

四、其他电源、地、信号啥的不知道你是做什么用的,也看不到很具体,不好说。不过可以看的出,除了FPGA其他芯片电源脚都没有安放去耦电容哦。

五、整个板子上没有看到大的电解电容,看到左上角似乎是两个数码管,这样在动态显示的时候,电源会有波动,恐怕电源不稳,导致工作不正常。

六、看到中间上面有几颗芯片感觉是同型号的芯片,摆放有一个翻转180度,感觉不是很好。看了走线,可以摆得一致。相同型号的器件排放方向尽量一致(光耦除外)。

粗略就说这么多吧,个人观点,仅供参考,不对之处,敬请指正。

总体画的还不错 以我的水平

是不是器件有点稀疏了

楼主水平比我厉害多了

如果不涉及保密 加上必要的丝印层注释也是可以的 这样也方便调试

那个同学指出了三点错误:

1 板子过孔太多,其实只要一半就能完成

2 整个板子的电容电阻安防没有规律,要么横着放要么竖着放

3 电源走线毫无规律,走的很乱,可能无法工作

板子画的对不对,先不说。从整体效果上看还是值得夸奖的。

我给你说说我的经历吧:

一名教授拿着我的一个小板子说:你的焊工很一般(我的板子是用mega48贴片的);这个电路太简单,大1的学生做做还勉强可以(是的,尽尽是2线制的电压表,电压从3.8到30V工作,3个数码管。)

我回敬到:您教书一定不错的,但是您会焊电路板吗?他说,我是做理论研究的。我又问,你做过什么项目呢?他说我的很多学生在什么什么单位做技术主管的。

我的同伴更猛:我们走吧,听喇喇蛄叫换我们还不种田吗?

教授很有风度的说:这两个孩子啊!

没过多久,他给了我几个他和他的学生们“不爱干”的小项目,当然我也表示很忙”不想干“这活,除非多给钱。 后来他无耐的答应了。

最后记住 “听喇喇蛄叫换我们还不种田吗?”

看起来还挺规则的

我不太同意这说法,我以前也是这么认为的。但后来发现做工程和做理论不一样(当然,前提是真正做理论研究的)。

工程讲究的是能实现功能,理论研究的的是如何更好的实现功能。从整体上来说,做不做得出工程和理论研究得怎么样并没有很大的关系,而且理论才更能推动科技的进步。。。

一家之言,仅供参考。

的确,说得没错

画板子是熟能生巧的技术,多画几次,自己都能感觉的在进步

尽量少打孔,走线尽量少拐来拐去,电源最好一目了然

PCB画的不错,我还没画过这么复杂的PCB 呢,

DIP封装的IC换成贴片的更好吧……呵呵……

电源尽量粗 一目了然 这个可以理解。

过孔尽量少 我感觉和走线正面横 背面竖有一些违背 也不能说违背 就是他俩有点冲突吧 呵呵

比如啊 如果板子布局非常紧凑,就必须尽量横竖交错的走线 这样过孔自然也少不了 我遇到过这种事 一个很小的地方斜着走了一条 结果就要付出更多的过孔来绕过去

个人观点 欢迎拍砖

呵呵,越到最后越难画,牵一发而动全身,所以我画板子经常画好几遍

总可以找到最优化的解决办法的

不用太在意同學的說法, 自己要有自信點, 貫孔太多 和 零件擺放美觀的問題, 隨著你的經驗增加, 自然會自我進化, 以目前你的經歷而言 此PCB算很好了

楼主这板子画得很好了!谁说的不好?!!晚上去抄他家!MD!有本事画出个更好的来!严重鄙视这种说话不负责任的人!!这种人走夜路很不安全的!!

你说的很对,我们的想法不矛盾。可是你看中国这么多搞理论的人都论出什么了?你做一块电路板,数一下,有几个国产件?你再看看有什么国产软件可以在世界上拿的出手? 中国有象样的航空发动机吗? 大的不说,你查查 7805、红外接收头里面的芯中国能生产吗?都说我们中国人善于模仿,为什么今天也没模仿不出个捷达车来呢。 各大院校、研究所的科研成果有几个不是花钱买来的。这样的一群人有什么资格对技术人员指手画脚的。 你看看国外那些得诺贝尔奖的,那才是真搞理论的。

说起来有些激动,你别笑话我呀!

一道测试题:

编个单片机程序“C语言让单片机端口1秒输出高电平1秒输出低电平,如此循环,单片机型号任意,半小时内当场在纸上写出来” 有兴趣你去考考那些名校的电子工程系研究生,看看有几个可以做到的。 我试过,90%的人做不到。

谢谢,看了以后深受启发,很有道理的,我们不能因为他人的言语之类的而耽误自己的正事,走自己的路。 谢谢。

我也受过很多人的打击,也伤心过。但是现在想想也许他们是我前进的动力。 我最解气的一次是上了一年多班时,我要求去工厂参观,单位同意了,我看见了上学时一直看不起我、曾经不可一世的同学正在埋头焊板子,我上去排一下他的后背说:咳!没想到我们又成了同事,我在开发部工作,他看着我瞪大眼睛很久说:你啊。 我在他面前表现的很傲慢,我现在的收入是他3倍还多,其它待遇更不是一个档次的,就凭这一点他还会看不起我吗? 我想老天会眷顾那些默默求上进的人的。你做的图可比我当初强多了,加油吧!

我不太同意12楼的说法,理论固然重要,但不能脱离实践空谈理论,当然也不呢能不看书本一味的专研所谓的技术。理论与技术应当是相辅相成,缺一不可的,无论脱离哪一个,那另一个一定不可能达到多高的水平。现在中国的高校里大多是空谈理论,多自以为我虽然不懂技术但我的理论可相当的强,而现实是只懂得些表面文章。21楼说考名校的电子工程系研究生们技术会有90%的人不会,我说考理论大部分的弱电类学生和部分老师同样也不行。。。根本原因是绝大部分中国的高校师生其学习是面向考试和文凭的,而真正的能成为科学家或工程师的学生或老师其学习是面向求知欲、面向工程、面向真理的。。。

画的不错,楼主不要气馁!有更好的点子可以学习啊

我觉得你同学3点都没有说错

经过多次布板是可以消掉很多过孔,毕竟过孔会影响信号的传输。

整个电源线的布局是需要改善。

FPGA下面的推偶电容最好离管脚进一点。但是不是非要横竖一直排放。

纯属个人意见。

正面走线和背面走线交叉防止耦合啊

这么复杂的板子我还没画过呢 向楼主看齐

还是你说的好啊!有水平。 不过平时还是不要谈论这样的事,小心被群殴。

我的感受是: 做技术的,如果对方是善意的说出问题在那里,我们每个人都会表示感谢。

http://bbs.eeworld.com.cn/thread-330157-1-1.html

这是我做的板子,也请大家去我的贴子上评一评,优缺点都说一下,别光说缺点啊!

我不是專業的Layout工程師,所以實在看不出來你的走線有啥不妥。

我只能說:洗出來就知道了^^a

不過,我見一你先把焊盤那一層用1:1印列出來,然後用實際的物品去比較,這樣比較不會出現洗出來的板子卻焊不上去的困境。

不過……洗一次可不便宜咧……

hi Linearfly,

我想请问一下, 为什么光耦器件可以不放规律? 还是一定不可以放的太整齐, 原因是什么? 谢谢

像楼主学习,水平还不及楼主

我非常支持前辈的看法。我自己画板深有体会,感觉想省事一点,就全部用两面相互垂直的线,用非常多的过孔,很容易一遍就布通了,但是布线完成之后就发现,板子会空好多,不怎么好。所以觉得画板子真是一门艺术,想寻求高稳定性+尽量少的过孔+尽量小的板子。。。

光耦多数时候用在信号隔离,信号有输入输出,因此,对于同一型号的光耦必然会有反向摆放的问题。如果都摆放一致的方向,走线的间距可能不能保证足够的隔离强度。必要时有的设计还需要在光耦下方的pcb板上开槽提升隔离强度。

谢谢, 解释的很详细, 拜谢了

是不是你没有铺专门的底层啊?冒失FPGA散热要求很高,估计要专门的铺地层GND

冒失他有丝印层在上面吧

嚣张哦!

再次看到这个帖子附上来,还是要鼓励鼓励楼主的。

1 好不容易花了一块fpga的PCB出来,给同学一看,说了3点内容,说板子太差,还说我画的板子太烂了。(当时我忍住了)

2. 谁能看一看我画的板子,有什么地方不好,我想知道那位同学说的是否属实,谢谢了。(铺铜隐藏了)

下面分别是 布线图+顶层布线图+底层布线图+FPGA部分 (双层板)

楼主画的还可以把,不知道那些细节是否合格呢,还是要鼓励楼主拿出来秀秀呀。

不知道板子大小是否规定了 器件有点稀疏

那个同学说的一点就是: 过孔多的一塌糊涂,其实只要一半就可以完成这个板子。 这话有有理吗?

FPGA的焊盘有点短,如果那是软件自带的库里的,那建议自己做个封装,否则焊时很麻烦;还有FPGA下面的电源走线太乱;某些器件的去耦电容和电感没弄,晶振的输出脚最好串一个小电阻;配置口太难找了,而且离其他元件太近,到时候会不能用牛角座。我也画了第一块FPGA板,出了不少问题,不过不出问题怎么能记住呢?

一、受力器件的焊盘最好包铜,比如DB9,电源,排针的焊盘最好包铜或加泪点。

二、如上同学所说,布局有点稀疏,可以再紧凑一些。

三、还有板子跨度太大,只有4个角有安装孔,担心插拔的时候压弯pcb,导致器件脱焊引起接触不良。

四、其他电源、地、信号啥的不知道你是做什么用的,也看不到很具体,不好说。不过可以看的出,除了FPGA其他芯片电源脚都没有安放去耦电容哦。

五、整个板子上没有看到大的电解电容,看到左上角似乎是两个数码管,这样在动态显示的时候,电源会有波动,恐怕电源不稳,导致工作不正常。

六、看到中间上面有几颗芯片感觉是同型号的芯片,摆放有一个翻转180度,感觉不是很好。看了走线,可以摆得一致。相同型号的器件排放方向尽量一致(光耦除外)。

粗略就说这么多吧,个人观点,仅供参考,不对之处,敬请指正。

总体画的还不错 以我的水平

是不是器件有点稀疏了

楼主水平比我厉害多了

如果不涉及保密 加上必要的丝印层注释也是可以的 这样也方便调试

那个同学指出了三点错误:

1 板子过孔太多,其实只要一半就能完成

2 整个板子的电容电阻安防没有规律,要么横着放要么竖着放

3 电源走线毫无规律,走的很乱,可能无法工作

板子画的对不对,先不说。从整体效果上看还是值得夸奖的。

我给你说说我的经历吧:

一名教授拿着我的一个小板子说:你的焊工很一般(我的板子是用mega48贴片的);这个电路太简单,大1的学生做做还勉强可以(是的,尽尽是2线制的电压表,电压从3.8到30V工作,3个数码管。)

我回敬到:您教书一定不错的,但是您会焊电路板吗?他说,我是做理论研究的。我又问,你做过什么项目呢?他说我的很多学生在什么什么单位做技术主管的。

我的同伴更猛:我们走吧,听喇喇蛄叫换我们还不种田吗?

教授很有风度的说:这两个孩子啊!

没过多久,他给了我几个他和他的学生们“不爱干”的小项目,当然我也表示很忙”不想干“这活,除非多给钱。 后来他无耐的答应了。

最后记住 “听喇喇蛄叫换我们还不种田吗?”

看起来还挺规则的

我不太同意这说法,我以前也是这么认为的。但后来发现做工程和做理论不一样(当然,前提是真正做理论研究的)。

工程讲究的是能实现功能,理论研究的的是如何更好的实现功能。从整体上来说,做不做得出工程和理论研究得怎么样并没有很大的关系,而且理论才更能推动科技的进步。。。

一家之言,仅供参考。

的确,说得没错

画板子是熟能生巧的技术,多画几次,自己都能感觉的在进步

尽量少打孔,走线尽量少拐来拐去,电源最好一目了然

PCB画的不错,我还没画过这么复杂的PCB 呢,

DIP封装的IC换成贴片的更好吧……呵呵……

电源尽量粗 一目了然 这个可以理解。

过孔尽量少 我感觉和走线正面横 背面竖有一些违背 也不能说违背 就是他俩有点冲突吧 呵呵

比如啊 如果板子布局非常紧凑,就必须尽量横竖交错的走线 这样过孔自然也少不了 我遇到过这种事 一个很小的地方斜着走了一条 结果就要付出更多的过孔来绕过去

个人观点 欢迎拍砖

呵呵,越到最后越难画,牵一发而动全身,所以我画板子经常画好几遍

总可以找到最优化的解决办法的

不用太在意同學的說法, 自己要有自信點, 貫孔太多 和 零件擺放美觀的問題, 隨著你的經驗增加, 自然會自我進化, 以目前你的經歷而言 此PCB算很好了

楼主这板子画得很好了!谁说的不好?!!晚上去抄他家!MD!有本事画出个更好的来!严重鄙视这种说话不负责任的人!!这种人走夜路很不安全的!!

你说的很对,我们的想法不矛盾。可是你看中国这么多搞理论的人都论出什么了?你做一块电路板,数一下,有几个国产件?你再看看有什么国产软件可以在世界上拿的出手? 中国有象样的航空发动机吗? 大的不说,你查查 7805、红外接收头里面的芯中国能生产吗?都说我们中国人善于模仿,为什么今天也没模仿不出个捷达车来呢。 各大院校、研究所的科研成果有几个不是花钱买来的。这样的一群人有什么资格对技术人员指手画脚的。 你看看国外那些得诺贝尔奖的,那才是真搞理论的。

说起来有些激动,你别笑话我呀!