图说微电子最前沿:最好的绝缘介质是什么?-就是什么介质都没有

时间:10-02

整理:3721RD

点击:

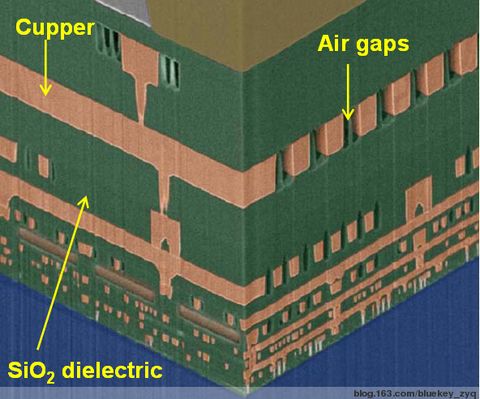

在集成电路中,将晶体管连接起来的是导线(如图中褐色的是铜线),将导线隔离起来的是绝缘介质(图中绿色部分就是最普遍采用的绝缘介质二氧化硅)。随着集成电路工作频率的提升以及导线之间间距的不断缩小,导线之间寄生电容对电路性能的影响越来越大。例如,寄生电容导致的线间交流耦合会导致互连线之间信号的串扰越来越严重;寄生电容的频繁的充放电会导致电路能耗的增加等。

如何减少导线之间的寄生电容呢?最简单的方法是拉大导线之间的距离,但这与集成电路尺寸不断缩小的要求相违背。所以,只能降低导线之间绝缘介质的介电常数。所以,寻找比二氧化硅的介电常数更低的绝缘介质(即所谓“Low-k”介质)就成为近年来集成电路领域的热门课题。

哪种介质的介电常数最低呢?就是真空,其相对介电常数只有1.0。但说起来容易做起来难,如何在最小限度地改变集成电路制造工艺的前提下,实现导线之间的真空隔离?最近,IBM发明的“气隙(Air gaps)”技术成功实现了互连线间的真空隔离。这种气隙实际上没有气,是在导线之间形成的真空管道(如上图所示),宽度只有20nm左右。

制作气隙的具体方法还不得而知,但据说制作气隙所带来的工艺成本的增加只有15%。IBM已经完成了65nm、45nm和32nm尺寸集成电路的试验,AMD则打算将此技术用在将于20092010年推出的32nm CPU中。

可见,只有想不到的事情,没有做不到事情,不是吗?

这个做起来太难了吧,居然用真空绝缘。。但是在高温条件下就不知道怎么样了。