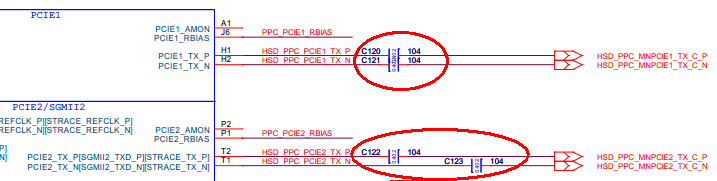

PCIE输出的差分时钟信号为何要接两个耦合电容?

隔直。0.1uF/0.01uF左右。PCIE的编码0的个数和1的个数是平衡的,所以其直流电平是稳定的,加电容可以使得输出和输入端直流电平被隔离,电平值不会相互影响也隔离外界直流干扰,至于芯片自身的偏置相关。

呵呵

thanks

路过学习

DC-balance技术在应用方面有很多的~

比如像HDMI的,SATA的,

但个人觉得还是隔直作用是首要的。这里采用0.1uF/0.01uF的电容关键是AC-coupled, 因为在常用的差分信号中,有三种结构我们较常见:pure differential-architecture,类似于SATA,PCI-E,一种是center-tapped differential-architecture,以太网上常见,另一种是Thevenin-architecture这三种的应用环境的差异在于客户的使用环境或是Recevier相关。

PCI-E中的0的数量和1的数量是否平衡,我不知道,没看过具体的sepc介绍,我只知道DC-balance的目的是为了减少0与1的数量之间的差异,达到一个平衡状态。

至于怎么取这个AC-coupled的电容,我人一些资料上看到的:取决于信号的总的衰减。

具体的应用环境要具体的分析了,线长的多少,连接器上的衰减,PCB上的一些杂散因素都是决定这个电容的容值的选取。

xiexie!

www.yiku555.com 扎金花游戏 扎金花 扎金花游戏

扎金花下载 港式五张

深海捕鱼 www.juleqp.com 砸金花游戏 诈金花游戏 www.999suoha.info 炸金花 扎金花下载 砸金花 诈金花www.yikusuoha.info 梭哈 梭哈平台 梭哈游戏 港式五张

只知道是交流耦合 学习下