cpu连接DDR3的地址线为何要串入33Ω的电阻?怎么取值?

时间:10-02

整理:3721RD

点击:

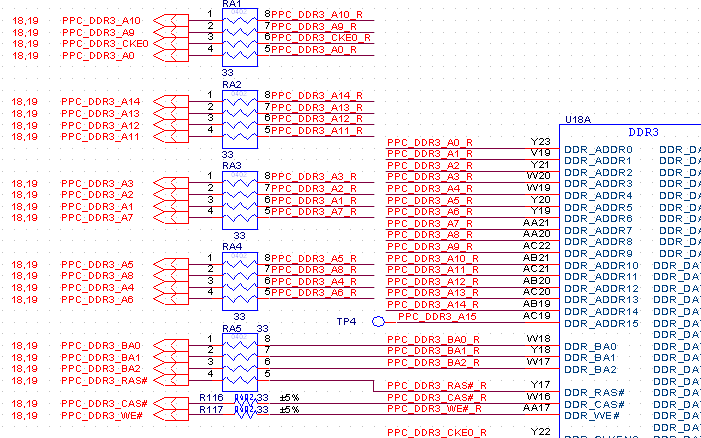

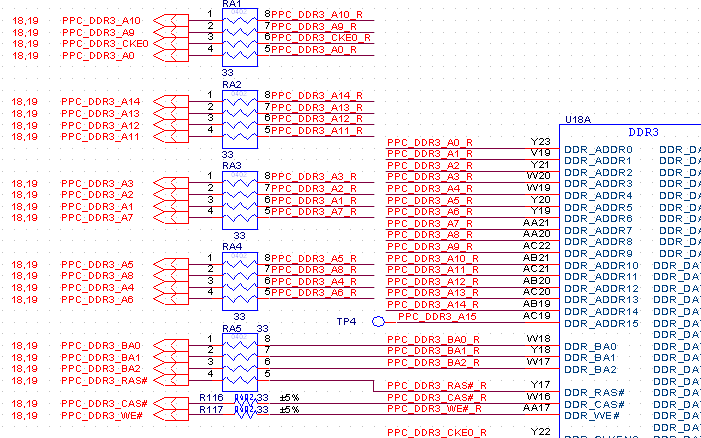

cpu连接DDR3的地址线负载端(DDR3接收端)已经进行了50Ω的阻抗匹配,为何在靠近CPU(APM86791)的驱动端要串入33Ω的电阻?怎么取值?请知道的高手们赐教!谢谢

源端串联匹配在一定程度上可以/有时也需要和终端并联匹配一起实施,对信号质量、功耗、EMI等都有影响,取值和实际芯片IO的输出阻抗以及信号负载等相关。

要选取最佳值,找到各个芯片的IBIS模型,搭建一个平台仿真一下吧。

要选取最佳值,找到各个芯片的IBIS模型,搭建一个平台仿真一下吧