DDR3仿真的疑问

时间:10-02

整理:3721RD

点击:

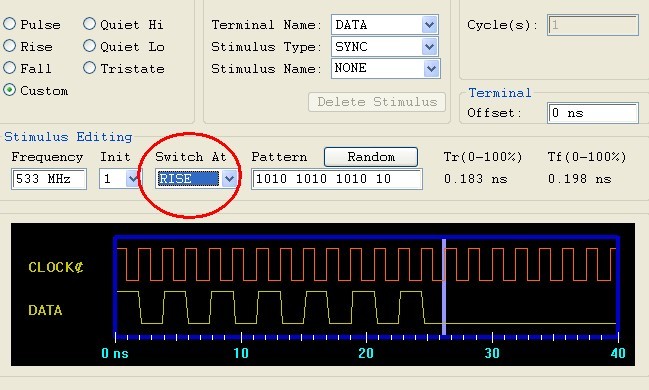

DDR3主频1066进行数据总线仿真时,时钟频率因设置多大呢?533MHZ吗?

file:///C:/Documents%20and%20Settings/Administrator/Application%20Data/Tencent/Users/303460919/QQ/WinTemp/RichOle/(1RFF039QO%60UFAQPRW~8%60_M.jpg

进行数据总线仿真,上图这样设置是否正确呢?

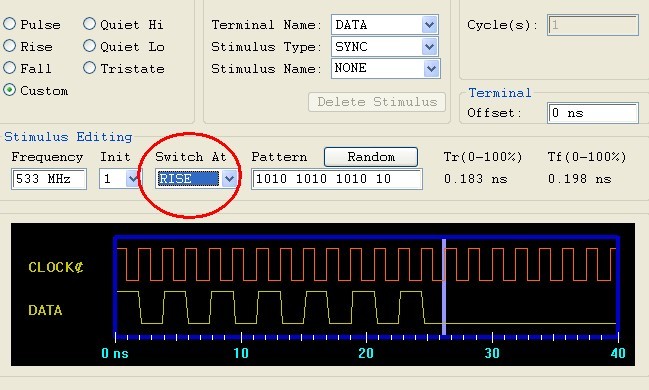

还有进行地址总线仿真频率也应取多少呢?是按下图这样设置吗?

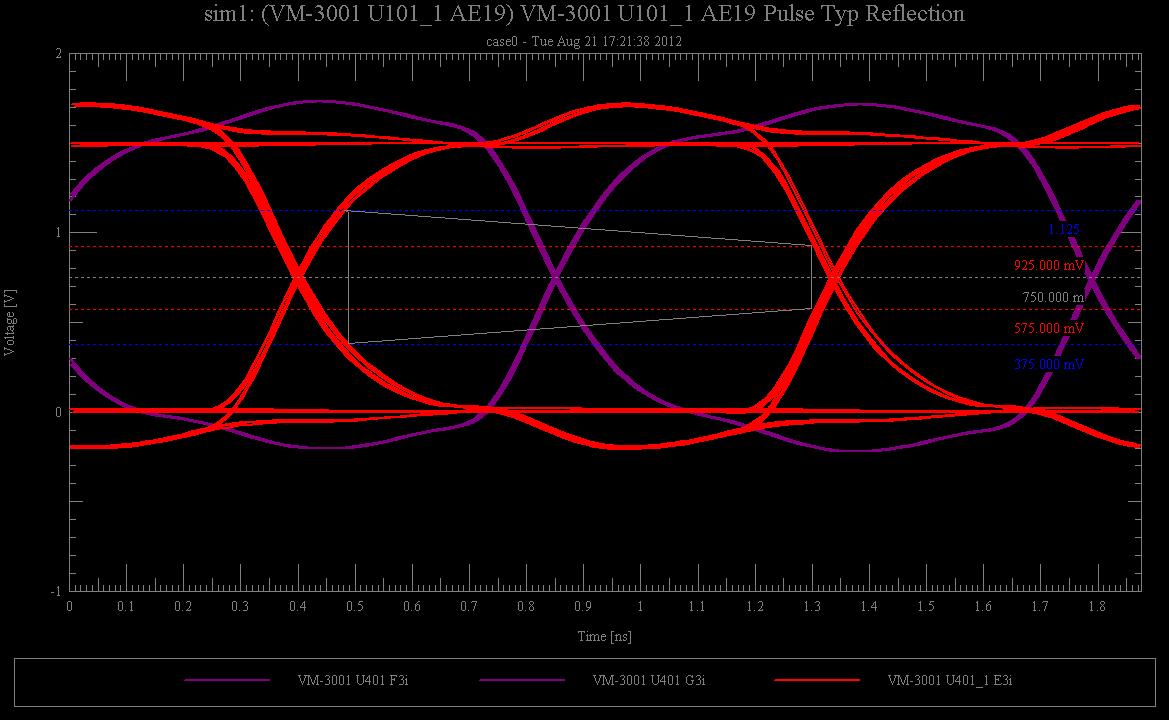

如果是CLK的SDQ信号,你应该用Pluse信号,频率设为533Mhz,从第四个周期开始看波形。

如下图:

按现在用Custom也行,选择重复的0101 pattern即可。在单端触发的时候,触发频率需要选择1066MHz。