DDR II 差分时钟线仿真疑惑

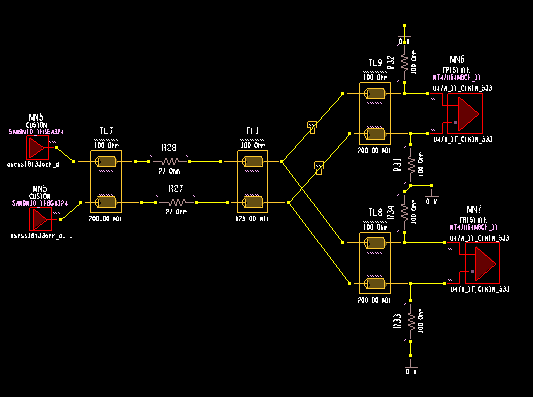

发送端波形

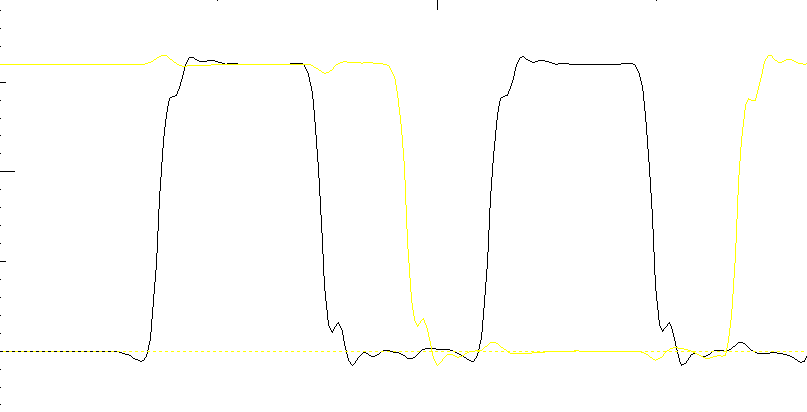

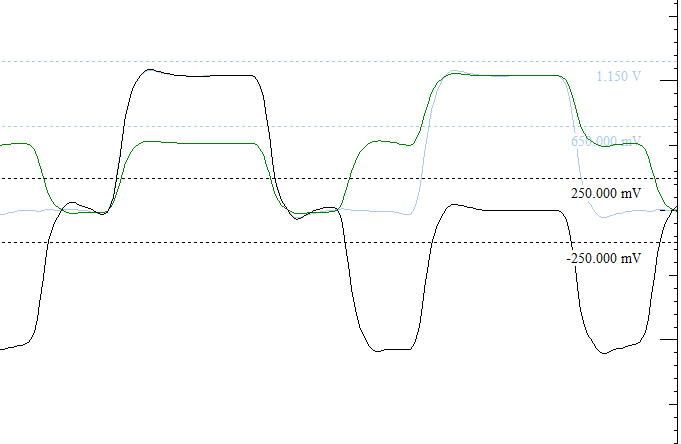

发送端波形 接收端 差模 共模 等信号波形

接收端 差模 共模 等信号波形问题如下

1)如果芯片本身有ODT IBIS模型应该包含在V/I曲线内,为什么仿真没有起到作用呢?

2)这种情况下我是不是要自己把终端电阻加上

3)其实 CK CK# 应该属于伪差分信号,并非互为回路,但是这种匹配的确能提高信号质量,仿真结果是否有参考价值?

没遇到过,看来要多学习

l小编在仿真这条路上已经上路了哈。

怎么沒人幫忙分析下呢

doltbird 发短消息

加为好友

doltbird 当前在线

UID69718 帖子99 主题16 精华0 积分431 经验3288 威望0 贡献2362 金钱420 元 宣传积分15 银行存款0 元 阅读权限100 性别男 在线时间32 小时 注册时间2006-4-5 最后登录2010-8-16

小编

帖子99 精华0 积分431 经验3288 威望0 贡献2362 金钱420 元 性别男 注册时间2006-4-5 2#

发表于 2010-8-4 14:49 | 只看该作者

回复 1# chenyaw

兄弟,简单的讲,差分信号不是这么仿真的。你的差分驱动模型就没有做好,不能用两个单端的模型来“凑”出差分信号。所以,第一步你要知道怎么来做个差分模型。第二步,要看你的器件手册,它会建议怎么来做匹配。你的驱动器用的是什么器件啊?

TOP

learning123456 发短消息

加为好友

learning123456 当前离线

晨

UID85281 帖子284 主题5 精华0 积分336 经验2322 威望0 贡献1862 金钱27 元 宣传积分0 银行存款1 元 阅读权限30 性别男 在线时间10 小时 注册时间2006-7-30 最后登录2010-8-10

中级会员

晨

帖子284 精华0 积分336 经验2322 威望0 贡献1862 金钱27 元 性别男 注册时间2006-7-30 3#

发表于 2010-8-5 10:43 | 只看该作者

静待学习了................

努力是必须的,关键是如何去努力

TOP

chenyaw 发短消息

加为好友

chenyaw 当前离线

UID102924 帖子64 主题5 精华0 积分203 经验1185 威望0 贡献1355 金钱22 元 宣传积分0 银行存款0 元 阅读权限30 性别男 来自河北 在线时间3 小时 注册时间2006-11-28 最后登录2010-8-10

中级会员

帖子64 精华0 积分203 经验1185 威望0 贡献1355 金钱22 元 性别男 来自河北 注册时间2006-11-28 4#

发表于 7 天前 22:27 | 只看该作者

驱动端是个ARM9 的DDRII 控制器,信号时 CLK 和 #CLK,这是器件本身的IBIS模型,并非我拼凑出来的,由于按照原厂推荐的匹配配置 仿真结果非常差,因此才疑惑的.

没有解决不了的问题!

TOP

chenyaw 发短消息

加为好友

chenyaw 当前离线

UID102924 帖子64 主题5 精华0 积分203 经验1185 威望0 贡献1355 金钱22 元 宣传积分0 银行存款0 元 阅读权限30 性别男 来自河北 在线时间3 小时 注册时间2006-11-28 最后登录2010-8-10

中级会员

帖子64 精华0 积分203 经验1185 威望0 贡献1355 金钱22 元 性别男 来自河北 注册时间2006-11-28 5#

发表于 7 天前 22:29 | 只看该作者

ATMEL AT91SAM9M10 + MT67H64

没有解决不了的问题!

晕,每人来帮我分析!郁闷!

查看手册中ODT的描述,是否CK有,另外对于CK一般是在颗粒侧跨接电阻进行匹配。

On-die termination: ODT (registered HIGH) enables termination resistance internal to

the DDR2 SDRAM. When enabled, ODT is only applied to each of the following balls:

DQ[15:0], LDM, UDM, LDQS, LDQS#, UDQS, and UDQS# for the x16; DQ[7:0], DQS, DQS#,

RDQS, RDQS#, and DM for the x8; DQ[3:0], DQS, DQS#, and DM for the x4. The ODT input

will be ignored if disabled via the LOAD MODE command.

对CK信号,一般是没有ODT匹配的,最好确认清楚,对CK信号,推荐使用跨接电阻的匹配方式,戴维南匹配要小心使用,因为会涉及到两个信号波形幅值的不同步,及电源噪声的影响