千兆以太网时钟线(125M)问题求助!

小弟正在调试一块有千兆以太网的板子,可是千兆网口就是不能用(10/100M没有问题),后发现是cpu送给网口芯片的125m参考时钟有问题,在板外通过一根约26cm(左右约1cm)的飞线就没有问题了(线长了或短了网口性能就下降直到完全不能用),我又重新布了一板pcb,将走线改为26cm左右,线宽8mil,可还是不行,

该线是cpu于phy之间传输数据的参考时钟,由cpu送到phy,由于在复位期间phy的该引脚要置为低(否则网口不可用),故使用244为该引脚在复位期间提供低电平!

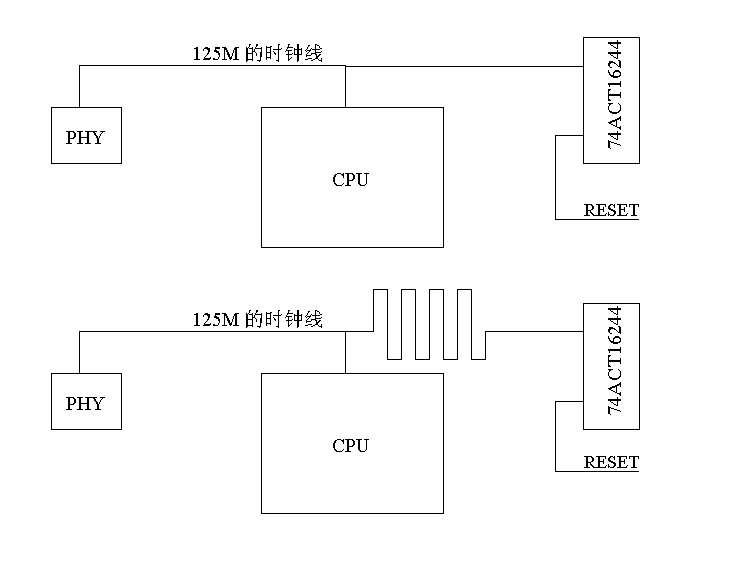

前后二板的布局和走线如下图:各位给点指示吧!这里先谢谢了!

采用什么接口RMII or S3MI?数据信号长度是多少?

看情况是PCB设计的原因了!

哈哈,搞定了,在cpu到244之间串了一个200欧的电阻就可以了,但电阻必须尽可能的靠近cpu一端的引脚,网口性能非常好,,后来我又做了测试,将该引脚通过一个200欧的电阻接地也可以,郁闷,

aixiao 老兄,应该也是pcb出了问题,可是现在用这种方法解决了,但是我还不明白为什么?可不可以给点解释!(是端匹配吗?)

接口是GMII模式,数据线长度都在50到70mm之间!

你当时没有用示波器去量量CLK的信号吗?

1.如果你的AGND处理的不合理,你的1000兆数据会有CRC错误的,甚至不可能导通.

2.不知道你的125M时钟是什么样子的,发张图片分析一下

3.根据你说的串联终端或并联终端都发现接口是UP的,其实这两种方式都是解决时钟线路阻抗的问题,减少时钟的反射,消除过冲,如果你能够找到更小的电容,并联端接也应该是没有问题的(假设你的CLK时钟效果确实很差的前提下)

主要是因为你的时序配合不上,加上电阻改变了时序和波形质量。

200欧姆说是改善si阻值也太大了一点,200欧姆已经是把信号沿拉得很缓了,逻辑上就是125M时钟被滞后,换句话说,到CPU时钟的延迟不够,走线还需要加长。对于GMII的信号,是标准的源同步时序,不但收发时钟是分开的,连数据线收发也是分开的,本来很容易处理,你八成是125M到CPU和PHY的分支没等长。

并不是所有的匹配都是小电阻的。电阻的大小和位置都决定了信号的质量。为什么用200欧是它的位置决定的。

他用的是串阻端接,请axiao用实例说明用200欧串阻端接是它的位置决定的,自己举实例也行,用小编的例子也行,我不爱听模凌两可的浑水话。这个问题的分歧是:在cpu端用200欧姆的串阻是si质量改善的作用大还是时延的作用大?

说那个作用大,那我也说不出来。因为这是相辅相成的,不是对立的。波形改善,对延时也有好处啊!

电阻的位置决定了他的大小。因为可以是匹配,也可以是限流来改善信号的波形了。只要做过几个产品,就会发现这个问题的。在源端,我们可以说是匹配,但在末端呢?自己仿真看看吧!

理论不一定能解释所有的问题。有些靠实践的了。有问题大家讨论讨论!

这里如果确实是增加了电阻200欧姆,限流是不能改善信号波形的,如果匹配电阻过大,那要看你该时钟信号的末端对地的容抗大小了,如果大,时钟的跳变时间长些,小,跳变时间基本不变,起到匹配终端的作用.

谢谢大家的讨论,

首先我用示波器测了125M时钟,由于使用的是最高只能测66mhz的示波器,所以观察波形的好坏很难,呵呵,条件限制,但能够大致观察该时钟,时钟上峰值1.2v,幅度200mv左右,(网口的phy芯片对于该信号的幅度要求是1。4V)

对于200欧的电阻,我看了大家的讨论后,又做了几次试验,用小于200的和大于200的电阻,以及在不同位置放着该电阻,结果如下,在放着200欧电阻的地方,放着电阻(大约)大于400欧或小于150欧时网口开始丢包,在远离cpu,靠近244的地方,放着电阻(无论是什么样的值)只能起到改善性能的作用(仍然会丢包),不能彻底解决问题

现在我想问的是,在这里串接,或到地的端接的电阻到底起到什么样的作用,波形改善,延时,或着谁的作用更大,

还有就是在网上看到许多关于高速电路仿真方面的东西,对于这样的设计能否采用一种比较简单有效的方式在制版调试以前发现这些问题,(我画原理图和pcb使得都是protell99)希望大家能给点意见!

学习中。