PCI板卡阻抗等效问题

我现在要做一个4层的PCI板卡,核心是FT256 1mm栅球FPGA接DDR,最小线宽6mil。

现在知道,上下2信号层、还有内电层,做成1盎司或者2盎司的厚度。

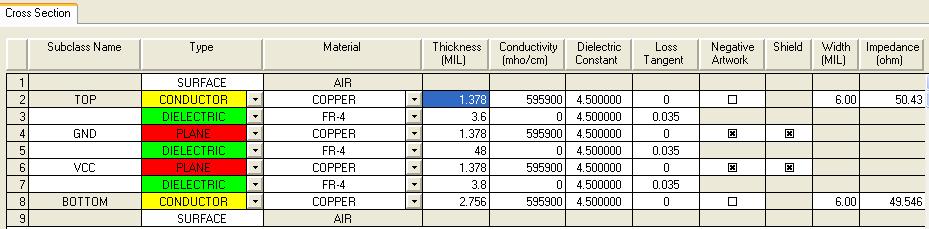

受制于6mil线宽,FR-4层厚度只能是3.4-3.6,以实现等效阻抗50ohm。如下图

为了,实现PCI的标准厚度63mil,就在地与电源层之间加宽了。这样做可行么?

其实你这个板厚是很典型的1.6的板子,(1.6mm=63mil),我也做过两块四层板,阻抗匹配到50 Ohm,一般地采用1.2mm的芯板即可,pp片采用1080+106=5mil,或2116=4.5mil,

需要提醒的是,介质厚度和芯板厚度不是任意制定的,常用的PP片,106(2mil)-1080(3mil)-2116(4.5mil)-7628(7.3mil),芯板有0.2/0.3/0.4/0.5/0.6/0.8/1.0/1.1/1.2/1.6/1.9mm,可以联系你的PCB厂家确认有关芯板和PP片的信息,也可以国内厂家“生益”网站查找。

具体的阻抗阻抗计算可以考虑用polar instruments的si8000,外层绿油和电镀厚也要考虑的,典型1盎司铜皮厚约1.4mil,电镀后可能达到2mil

太感激了。这正是我想知道的。我想接着问一下,PP片,106(2mil)-1080(3mil)-2116(4.5mil)-7628(7.3mil),前面的数字代表什么?因为我看到还有15mil。是6*1060+1080么?

"外层绿油和电镀厚也要考虑的,典型1盎司铜皮厚约1.4mil,电镀后可能达到2mil"

电镀是镀金吧?我记得建议说是0.25微米,外层绿油怎么说明?在Cadence里如何设置啊?这2层都算到顶层和底层?