AMD要求DDR1时钟差分阻抗120欧,是不是有点困难啊!

看的是LX800的layoutguid 单线阻抗5mil 60欧差分120欧,这个120欧的差分阻抗,感觉有难难达到阿! 叠层 按 S (2116) G (CORE) (2116) S

有经验的兄弟们说说你们怎么会怎么处理这个问题?

应该没有问题,可以有2种办法:

1、减小差分对的线宽

2、保持差分对的松耦合,则差分阻抗约等于2倍单端阻抗

用4mil的线宽7mil的线距算出来差分阻抗大约为104欧 3on7差分大约是113 5mil线宽 用si8000就基本上算不出符合要求的线距了

看过资料好像是建议差分对线距最好控制在7mil以内。不知道内存条上的时钟差分阻抗走的是多少?

比如intel一般ddr时钟差分阻抗是70欧,amd差分阻抗是120欧,插的是相同的条子,这样岂不是阻抗不连续了/

各位高手说说看?

如果是在是没法做到完全一样,那做到尽量接近是不是可以呢?

减小单条线宽,增大一下间距,层叠结构看看行不行

test

理论上, 单线阻抗60欧差分120欧,要求这对差分线没有任何耦合。实际工程上可以做成单线阻抗60欧多一点,差分间距大一些(耦合小),就可以做到差分120欧。

呵呵!其实你仿真一下就可以解决intel和AMD的不同了

其实你可以用PolorSi8000(算阻抗软件)计算一下就明白了。

增加层叠厚度来解决。

学习

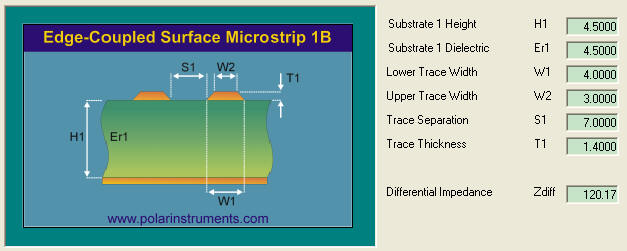

小编是不是做主板的呀?一般主板的单线线宽5mil,阻抗要求控制60欧。4mil线宽、7mil的间距,用SI9000算出来的差分阻抗正好是120欧。

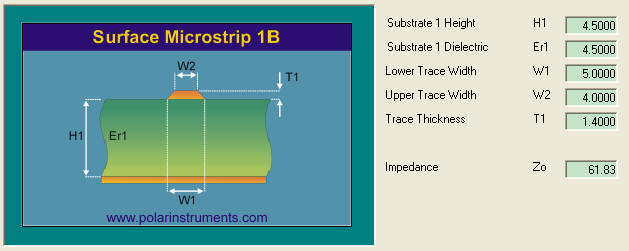

单线如下图:

差分线如下图:

楼上算得是按照不加绿油计算,实际计算得到的值,应该减去一定值,比如8欧左右