cadence SI仿真问题请教

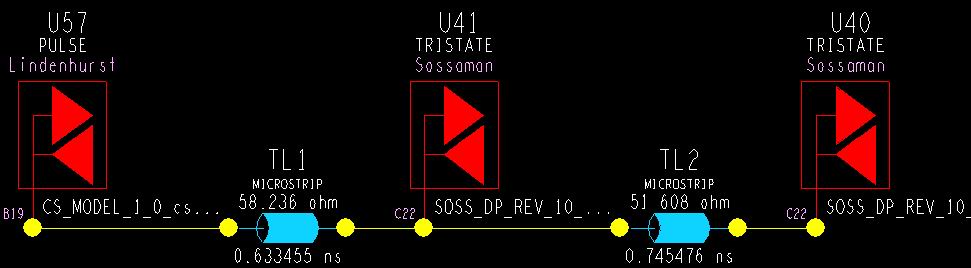

如图,u57是驱动端(pulse),U40、u41为tristate。实际工作中,u57给U40或U41任意一个发送数据时,另一个将是高阻态。我要请教的是:

1,当前是不是U40和U41都是接受?

2,怎样设置U40和U41一个是接受一个是高阻?

1,当前是不是U40和U41都是接受?

是

2,怎样设置U40和U41一个是接收一个是高阻?

没必要设置,接收的时候就是高阻。一旦设为高阻就是接收。

如果接收端是高阻,那不久不可能阻抗匹配了吗?

如果接收端是高阻,那不久不可能阻抗匹配了吗?

所以,一般情况下外面要加匹配。

这个拓扑是FSB的仿真,没有匹配电阻。我的方法是删掉U41,这样跟高阻可能更接近,但不知道是否有错误?

这个拓扑是FSB的仿真,没有匹配电阻。我的方法是删掉U41,这样跟高阻可能更接近,但不知道是否有错误?

不能删除,其实并不是真正的高阻,从ibis模型可以看出有几pf的电容(还有一些别的效应)。

在CADENCE里接受的器件是可选的,不需要你那么麻烦,在sigxplorer-> analysis preferences 里measurement mode ->receiver selection 里选 SELECT ONE

谢谢。但是一个设为receiver,另一个是什么状态?我还想了一种极端的情况:网络上有m+n+1个器件,1个驱动,m个接受,n个高阻那怎么办?

是呀,很有道理,感觉删除是不应该的,尤其后仿真时cadence可以对多个网络同时生成reports,waveforms等,不可能一个一个去删除。

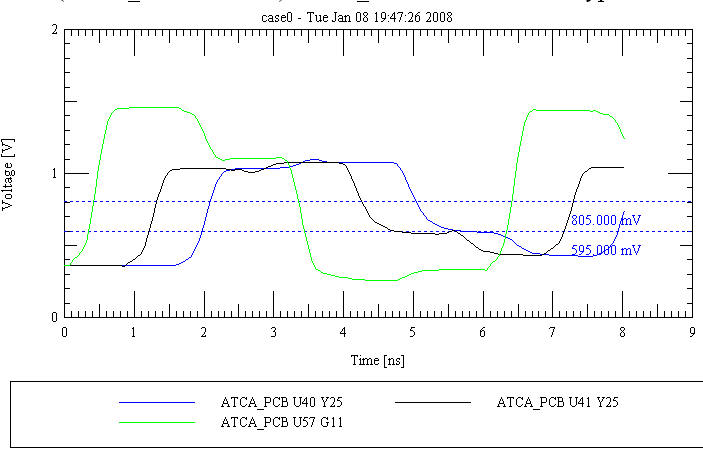

下图为U40、U41都作为receiver,U57、U41、U40的波形 (激励为167MH Pulse)

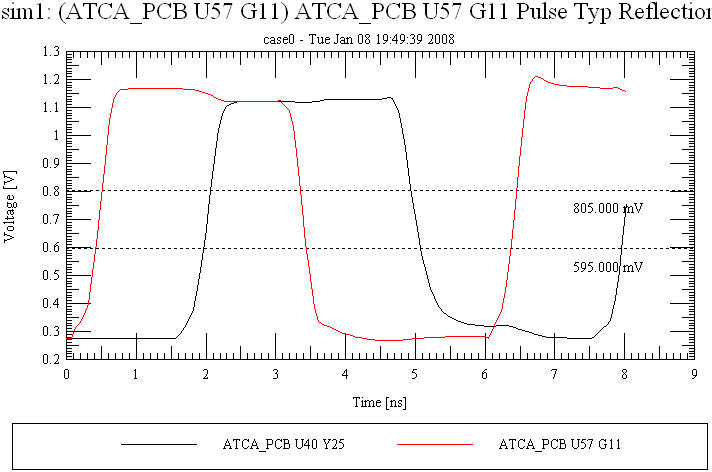

下图为删掉U41后的波形 ( 激励为167MH Pulse)

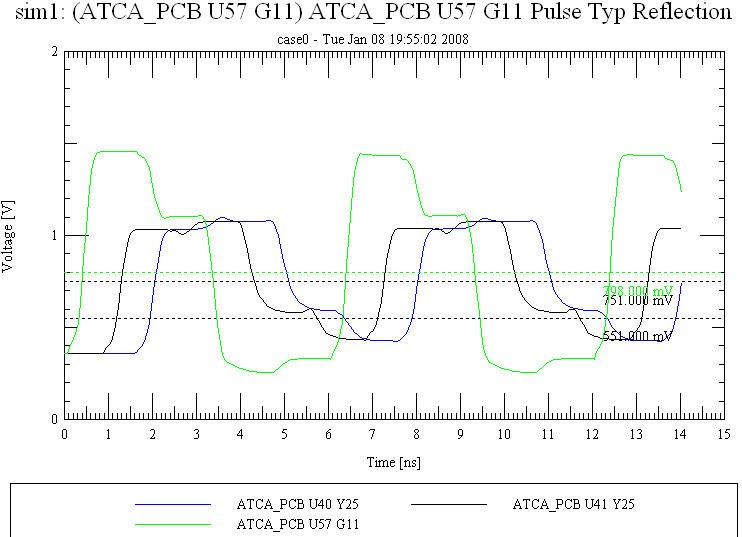

下图为通过select one 选择U40为receiver的波形 (激励为167MH Pulse)

他们怎么差距这么大呀!

谁能帮我分析一下!不胜感激!

上面的门限值 595mv、805mv是我根据芯片手册算的,然后加到图上的。最后的一幅图是仿真的原始图(没有更改VIH_L、VIL_H)---图中这两个值怎么来的?

仿真没有问题,但是有可能和总线的工作方式有关。

譬如时分复用总线可能存在冲突,从而不能采用软件自动仿真。

图一:正常啊,U40是没工作,U41波形正常,仿真软件还是正确的。

图二:估计也正常,你把U41关了(没选),U40工作,但是不管你是怎么样的器件(高阻)

U41对整个信号线路(姑且这么叫吧)还是有影响的,在U41处是阻抗不连续点,那表现在信号波形上

就是信号产生反射,在发送端就会看到上冲,(反射电压和发送电压叠加拉)在接收端一开始有点幅度下降,这些都是一次或多次反射的结果,至于准不准,事实是不是这样,那就不好说了,仿真嘛,还能怎么样?

你采用的是菊花链的拓扑结构,在高速信号下是会有这样的问题的,在实际中,发射端的信号不用管,有上冲没关系的,主要看接收,你U40的信号不是还好嘛,就是低电平时间短点,估计不影响接收采样(这个你要具体器件具体分析)还有,你做的是前仿真吧,如果等LAYOUT完后有过孔什么的波形会更差的。

恩恩,就这样拉,本来写了很多分析的,但是机器死了!再次写就没激情了。

PS:本人新手啊,有什么不对的地方或有更好的,详细的分析请大牛们指正啊!

非常感谢您的回复!出差一周,刚刚回来。未能及时致谢。