请教自激问题

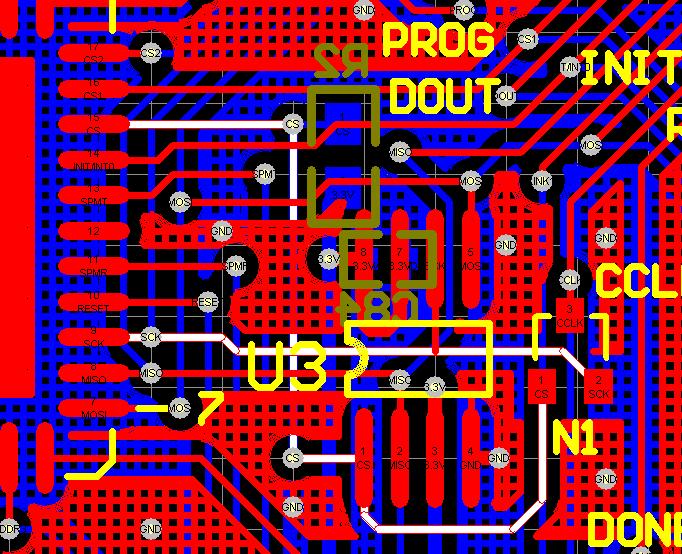

我想是CS引起的,你的走线存在问题!

CS的走线尽量不要从芯片的引脚板卡底层走线,这样很容易出问题!

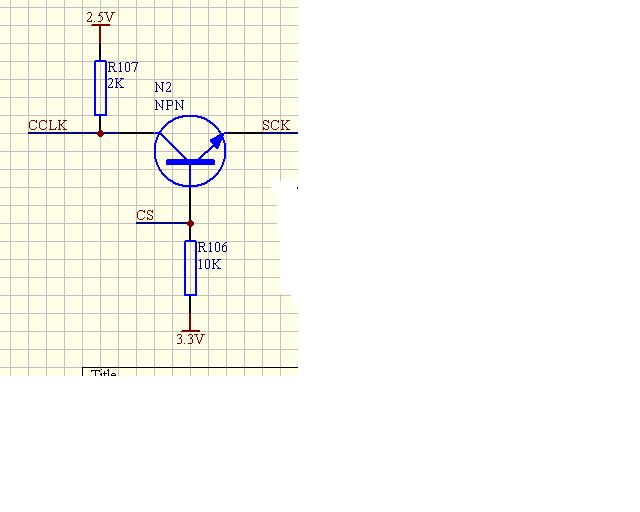

其实没每个引脚上的可以认为有1个寄生电感和寄生电容,我想这个原因是不是因为地弹引起的!能不能焊接一个0电阻试试看看!如果有测量设备,可以测量一下,芯片的引脚端的输出信号与0欧姆电阻端的信号,可能这个电压的毛刺会比较小,如果上了近100~200mv左右,就有可能存在,猜想而已!

小编能不能在CS端串上一个小的电阻,在10欧姆左右最好,精度为1%!串10欧姆的电阻的目的,是想验证有没有可能存在信号的反射!其实我仿真CMOS的反射时,发现在 驱动端端接一个较小的电容10pF比较好,特别在信号的上升与下降 延!

不好意思问一下楼上的

这句话是什么意思啊

谢谢Achilles_hu,另外再请教Achilles_hu:cs串个电阻是接地还是和射极sck相连?我一直以为cs只作为片选,布线可以不那么严谨。

解决了,在Achilles_hu 的提示下,在cs和基极间串了个电阻。谢谢Achilles_hu。

谢谢,你 让我发现了一个小的问题!能不能给我一个小的信息, 你的频率是多少?我想验证一下你说的这种情况,用模型仿真一下,如果能告诉我具体的芯片的型号也行的。

我的时钟频率是3M左右,三极管是npn3904,单片机是sst的89v516,fpga是xc3s250e,pq208封装

另外问一下Achilles_hu兄,你用的是PSPICE吗?

不是的,我用的是理论!加信号的仿真经验!

虽然你用的频率低,但我想门电路上的毛病总是相通的,所以给你一个建议了!

还有设计经验,你的走线确实这样走不太好,如果是高频的话,你那写引脚肯定有问题的!

但你不是的啊!呵呵,所以我觉得信号上的反射的存在也有可能存在的.串一个小的电阻就是为了减小反射的啊!

特别是的通用I/O口!

嗯,再次谢谢Achilles_hu

楼上的如是2 layer板,那么cs从ic下走就有问题了;若多层则无碍

顶.