IBIS模型没有测试负载,可是仿真却有buffer delay曲线,何故?

时间:10-02

整理:3721RD

点击:

我在用cadence sq作SI仿真的时候,驱动端IC的IBIS模型中并没有测试负载,但是仿真结果驱动端IC有buffer delay曲线。

不知道这个buffer delay曲线怎么来的,百思不得其解。

而且,测试负载不能确定,仿真结果也没啥太大的意义。

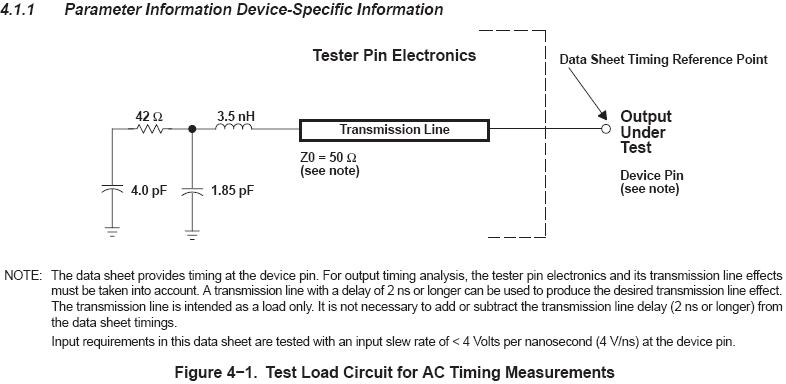

芯片手册给出的测试负载也比较奇怪,测试负载怎么会有电感,还有传输线,很费解,如图。哪位大侠给指点一下。

同疑问,希望知道的朋友帮忙解答一下!

能否把你的波形贴出来

就是个buffer delay曲线,方波信号,没啥看的,IBIS模型里也没有测试负载,

不知道这个buffer delay曲线怎么来的?

我想问一下你buffer delay曲线怎么观察到的

sigwave里面左边一栏以bufferdly为后缀的信号,右键,display,就可以了

仿真实验了一下,发现如果IBIS模型没有测试负载的话,buffer delay曲线就是没有测试负载时的情况。

编辑IBIS模型,修改测试负载和手册一致就可以了。

可是芯片手册给出的这个测试负载让我有点晕,不仅有电感,还有传输线。

也可能是我对这个测试负载没理解清楚

顶