信号上升时间由什么因素决定?

如上图所见:

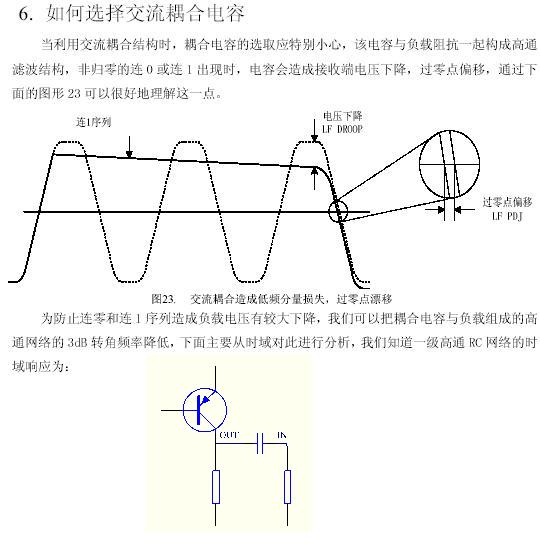

我们知道对于负载端,信号经过一个高通滤波电路,不短放电,并且拥有一个时间常数。同时也就确定了其的下降曲线(图中那跟缓慢下将的曲线)

我的问题是,对于信号发送端,确定信号上升时间的时间常数又是由谁决定的呢?

是不是和晶体管的饱和截止速度有关?

你提供的资料与提的问题没有根本关联。

偶合电容对与交流信号来说,阻抗为1/(2*3.14*f*c).因此频率越低,阻抗越大。但对信号上升沿没有影响。你可以自己算算看。

但与原来的输入信号相比,信号延迟还是有的。与R,C 有关。

对呀,我就是指的你说的信号延时哦。如果我用标准的方波,经过这样的电路它的信号上升时间一定不是o,对吧,我就是指的这个上升时间和谁有关?

方波用付立叶公式展开后得到各种不同频率的波形叠加。不同频率的信号经过C 时,阻抗不一样,延时也会不一样,但每种波形的上升沿并不该变。因此,他们通过c 后再叠加的波形一定不再是方波,而是具有了一定的上升沿。上升沿与输入波形,R,C 相关。

我记得有个式子Tr=(Tr1*Tr1+Tr2*Tr2+。+Trn*Trn)1/2(开方)不知对不对。

davidfu_2002,你说c我认为是耦合电容,那么R呢?我认为应该不是负载电容!

tpp,你说的公式中每个TR是什么意思?

davidfu_2002,你说c我认为是耦合电容,那么R呢?我认为应该不是负载电容!

tpp,你说的公式中每个TR是什么意思

信号经过 Tpd 到达电容时,电容瞬时短路,造成负反射,经过 RC 指数曲线充电,所以就会减缓上升沿。

输出阻抗,以及对应的负载阻抗的综合。

输出的上升时间除了与输出驱动器有关外,应该和所接的负载有很大的关系,媾和电容应该不会改变任意一给顶频率波形上升时间(也不会有除了本身反应延迟之外的延迟),如前面一位老兄所说只是不同频率的波通过后的衰减程度不同,叠加后改变了上升沿的波形。

方波是无数奇次谐波的叠加, 在经过容性或感性网络或到达具有容性或感性的负载时, 其频率不便但幅度和相位的相互关系却发生了改变,由此引起上升沿或下降沿的改变, 即使没有电容和电感, 对于高速信号来说, 铜导线也具有一定的特征电容和电感, 电容PF量级,电感NH量级

对输出一个方波来说,它的上升沿到了外电路以后,对于外电路来说应该是个一阶RC电路的零状态阶越响应。把整个电路等效变换为一个一阶RC电路(把前级输出电路的等效变换为一个电压源和电阻,后级输入电路的等效为一个电容,值为它的输入电容)。此时根据RC电路零状态响应方程,可以求出上升沿和时间常数的关系为:Tr=2.2RC.所以上升沿和电路中的电容(包括传输线电容,负载电容等等),电阻(不是绝对的电阻值,要看各个电阻的串并联关系,算出最后的等效电阻)的大小有关的。

另外Tr=2.2*R*C这个公式大家可以注意一点。high speed digital desighn里好像也提到过。

看看

了解!