via的擺放規則

时间:10-02

整理:3721RD

点击:

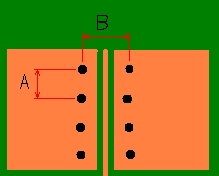

如圖所示, 若trace width=10mil. distance=10mil, impedance=50 ohm, data rate=5.0Gb/s (frequency=5.0G/2=2.5G)

請問A與B的距離該設多少?

若假設Er=4.2, 可求波長 3E8/[2.5E9*(4.2^0.5)] 約為58mm或2300mil

A項 若取波長的1/10以內, 設計為200mil, 不知是否適當?

B項 小弟就不知該怎麼取捨, 希望大哥賜教. 謝謝!

[求助]via的擺放規則

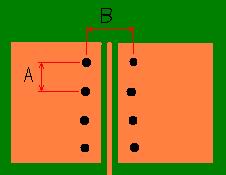

从串扰考虑b的间距最小咬70mil(孔的边沿间距)线到孔距离设置成30mil,间距a应该对间距要求不是很严格,只要不要把平面打断就可以了

老哥可以敎一下要怎麼計算嗎? 謝謝!

走线与周围包地铜皮的距离大于3h(h为信号线与参考平面的距离)就不会对走线的阻抗产生什么影响。如果减小到1h,走线阻抗会减小一点,可用polar计算一下,但增加了隔离度。从EMC的角度,推荐1h。屏蔽过孔焊盘只要不超过铜皮的边缘就行,越近越好。

至于A,我们公司一般至少是按λ/20的间距打孔,所以推荐A不超过100mil。