大家来看看这个时钟线走线好奇怪!

第3页有其他的走线图,大家看一下

第3页有其他的走线图,大家看一下

对了,这里在说明一下,这是一条SDRAM的时钟线,时钟频率是133MHZ

蛇形线增加延迟,保证时序的匹配

不会吧?!时序延时完全可以在软件中完成,这样的走线有背与高速走线的常理啊!?

保证时序

我也认为是延时

你所谓的常理是什么?

我说的“常理”就是:时钟线要尽可能走直线。我之所以对那个蛇行时钟线纳闷是这与因为我们公司以前布的板太不一样了。以前我们也布过一个类似的板子(与之有区别的就是:那次时钟信号频率是96MHZ),第一次画板的时候由于布局的问题导致这条时钟线走个大弯,结果导致该系统96M的总线频率始终跑不起来,第二次画板围绕着时钟线的作了调整,使其基本是是直线走线,结果就消除了这一现象。后来从MOTOROLA弄来的高速布局设计指导资料上也看到了对该信号布线措施,和我们改进的方法一样。但是这回看到的这块开发板的时钟走线却是这样的,所以使我感到困惑。

一年招蛇咬,十年怕井绳啊

----------------------------------

可以把你第一次绕的线贴出来给大家看看吗?绕也是有很大学问的,绕不好会有串绕会造成大的环路等等

这也算给大家一个一起学习的好机会

偶晕,这问题就不用讨论了吧,现在的时钟线不这样走的几乎没有了吧

对时钟线的长度有要求 主要考虑时钟的延迟 如:PCI 板的时钟线也是如此 蛇形走线

以下是引用szc1983在2005-11-8 8:53:25的发言:

一年招蛇咬,十年怕井绳啊

----------------------------------

可以把你第一次绕的线贴出来给大家看看吗?绕也是有很大学问的,绕不好会有串绕会造成大的环路等等

这也算给大家一个一起学习的好机会

也不是怕井绳拉,只不过是觉的时钟线应该是走直线而已。不过楼上各位说的延时,根据带状线传输延时公式:TPD=85*E0.5 (ps/inch)E为介电常数,再根据实际布线空间,按最极端的做法推算:该时钟线走线最短为0,其他走线最长1.574inch,延时也只相差大约184ps。这一百多ps的相差用蛇行线似乎多余吧?以上只是本人的想法,如有错误希望大侠指出

对了!第一次我们画错的那块板子,那个时钟线走线没什么特别讲究的绕,只不过是想用最短的线将两个芯片连连起来而已,此外就是注意了一下平行线间距。

时钟线的时序要与数据线相匹配,小编应该说明数据线是否也是如此走线,而不是单单拿一要时钟线来说明问题。时序如果不对,再直也没用

主要是增大tpd,减小信号反射造成时序的混乱。确保 2tpd<tr。纯属个人意见,欢迎大家一起讨论。

蛇形走线除了考虑时钟的延迟还有啥?

有意思!

同意13楼的说法,不能把时钟线单一的拿出来看。

是为了和数据线地址线等长控制

哈哈,现在的DDRII800的时钟线照样走蛇行线

蛇行线并不可怕,只要遵照设计规则就好,避免串扰,

何况蛇行线的平行段看起来像差分线,差分线的好处多多

在很高频的情况下,比如射频和微波,蛇行线可能引起时序问题

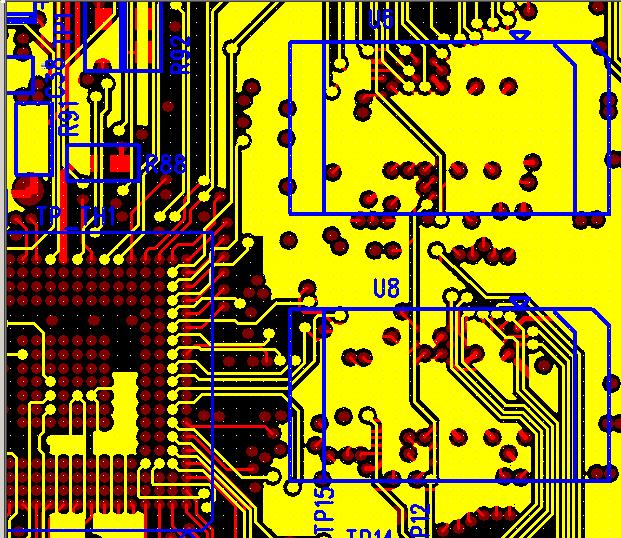

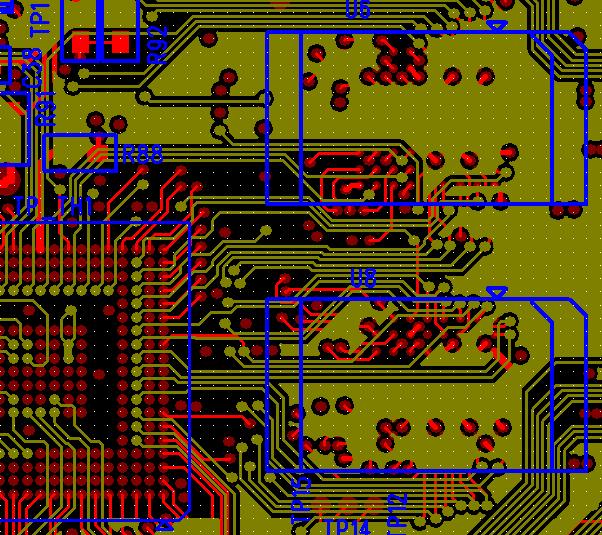

我现在手里的这张图纸是GERBER文件(我是用CAM350打开的),没法具体测量相关线的长度,而且没有NET,所以只能大概看一下。下面我把与这个时钟信号相关的信号线走线图给大伙瞧瞧。以下图中左侧是一片32bit微处理器,右侧两片是SDRAM。微处理器与SDRAM之间的信号线主要是:SDCLK、地址线、列地址始能(CAS)、行地址始能(RAS)、写始能(SDWE)、片选、数据线、DQM。

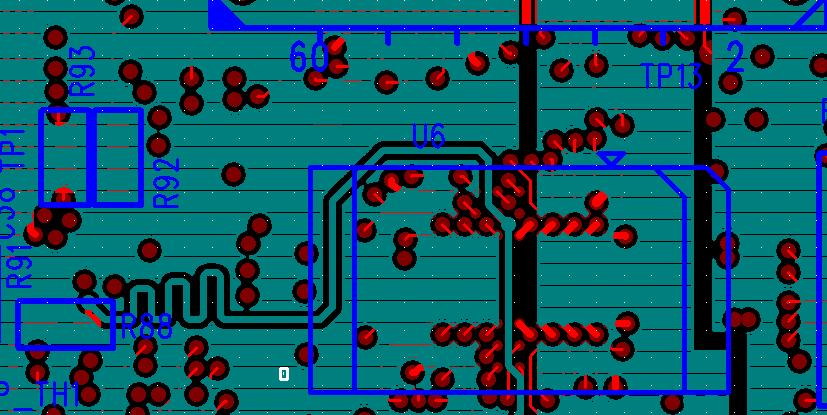

这是我感到奇怪的SDCLK(时钟线)的走线图。从中大家可以看到微处理器与SDRAM的外围轮廓,与SDRAM相关的信号线主要集中在微处理器引脚的右侧。

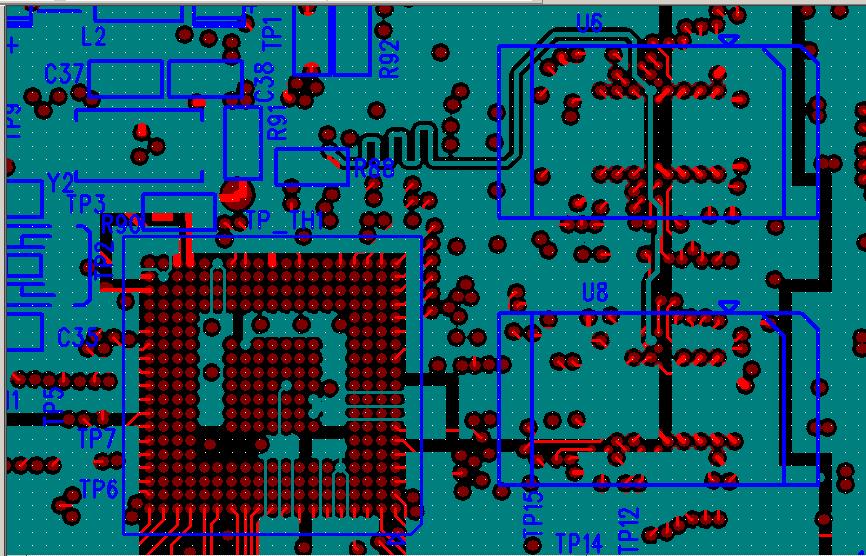

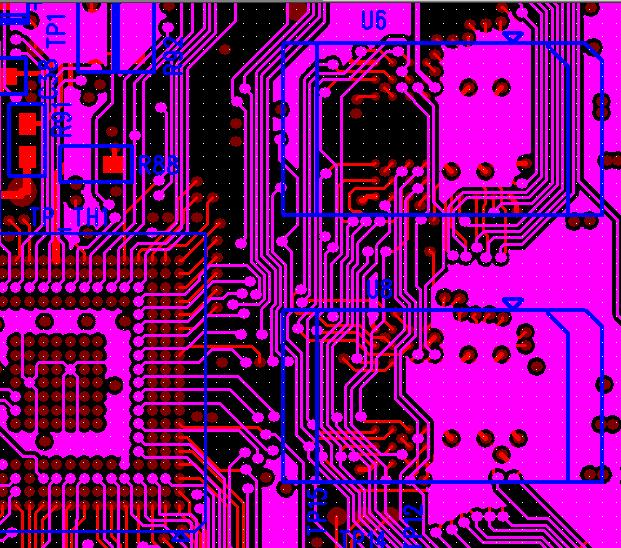

这层走线主要是地址线

这层主要也是地址线

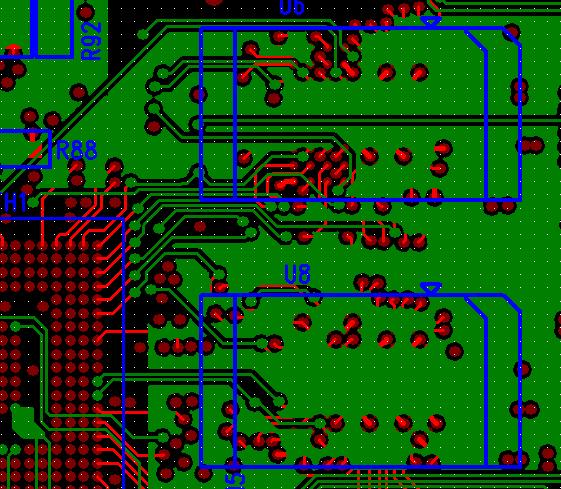

这层是部分数据线以及控制线

这层也是数据线与控制线

本人理解关于,蛇行线无非就是两个用途:延时或等长。但是从上面的图中的走线看,不像是走等长线。如果是起延时作用,那么在实际走线中以何为设计标准呢?本人研究了一个多星期,还是没有明确的答案,希望大伙也来发表一下看法,谢谢!

看了半天也没明白。

算时序就知道了

主要考虑的是CLOCK SKEW 要小,

这种模块我们公司经常做的,不知道为什么,反正做法就是数据线一组等长,有时候如果比较多就8位一组,组内等长100mil,组间300mil,地址一组等长,控制信号一组等长,然后时钟线clk和cke要比所有的线长,所以时钟线是一定会被绕的,具体为什么我就不知道了